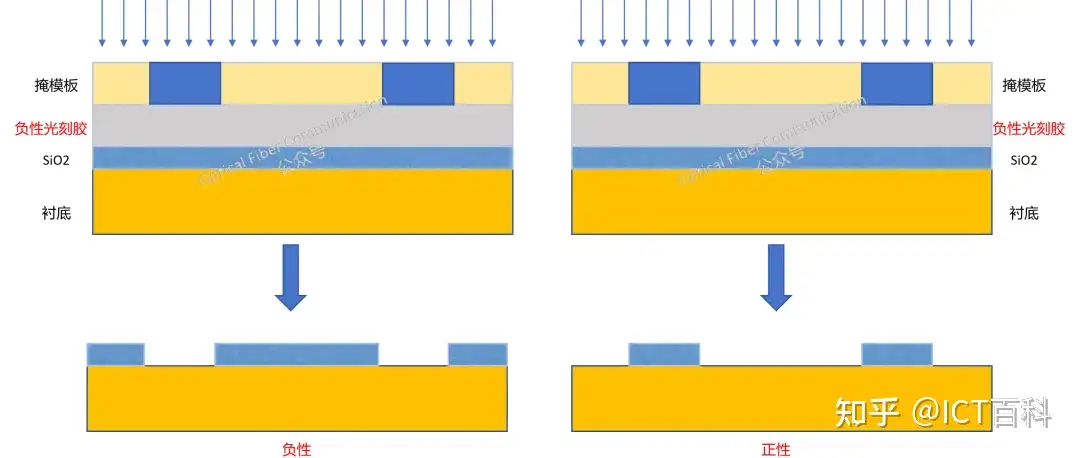

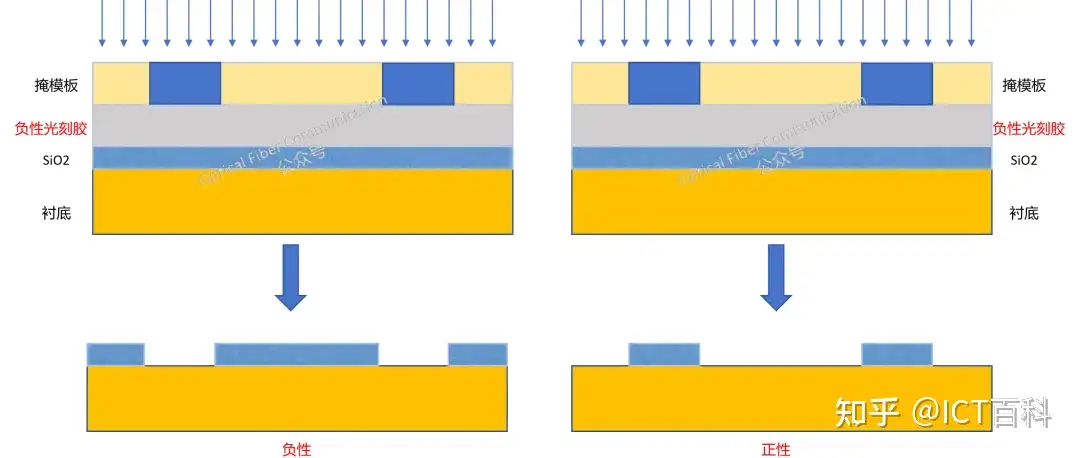

在前天我们的文章”到底什么是掩膜板?“中,说到掩膜板类似老式相机的”底片“,其实光刻领域还有类似于我们”相纸“的东西,即”光刻胶”。 光刻胶涂布在晶圆上,然后对其进行照射曝光,可以将底片上的图形”拓印”到”相纸”上。

光刻胶有一个比较正式的名字,叫光致抗蚀剂,英文Photoresist,简称P. R。所以在有些地方看到”抗蚀剂”也要知道它指的就是光刻胶。另外,根据它在光能量束照射下反应的不同[……]

在我们的社群有问到“减薄工艺与CMP”方面的问题。表面去年,CMP也有减薄的作用,但其实不太一样,另外还有一个磨削研磨的工艺,可能也会有所误解。下面我们放在一起来聊一聊。

为了更直观的展现这几个工艺的不同,我们先看看它们在制造流程中的位置,画了一个包含部分流程的示意图,如下。

图中的黄色底是磨削/研磨工艺,绿色背景的是CMP平坦化工艺,红色底的是减薄工艺。可以看出,在流程顺序上,它[……]

SMT(Surface Mount Technology),即表面贴装技术或表面组装技术,是直接将电子组件(如电阻、电容、集成电路等)贴装在 PCB 的表面上。它在电子组装阶段常见,同时在芯片贴装工艺上,SMT 也可以用于将封装后的芯片安装到 PCB 上。

图:SMT 贴装

与之对比的通孔技术 THT(Through-Hole Technology),则是比较传统的,它是将电子组件[……]

半导体的重要性就不细说了,大家可以想象到的日常生活中的所有电子产品都有使用到半导体器件。

其中,我们对这些产品最关心的一个共性指标就是:这货到底能用多久?

这个问题我们能否让用户帮我们检验?当然不能,除非是一锤子买卖。

为了产品在市场上不尴尬,就得从产品的可靠性说起了。也就是需要做芯片制造中三大测试之一的可靠性测试。

那什么是可靠性?引用某个规范中的一段话来说:[……]

经公众号Optical Fiber Communication同意发布。

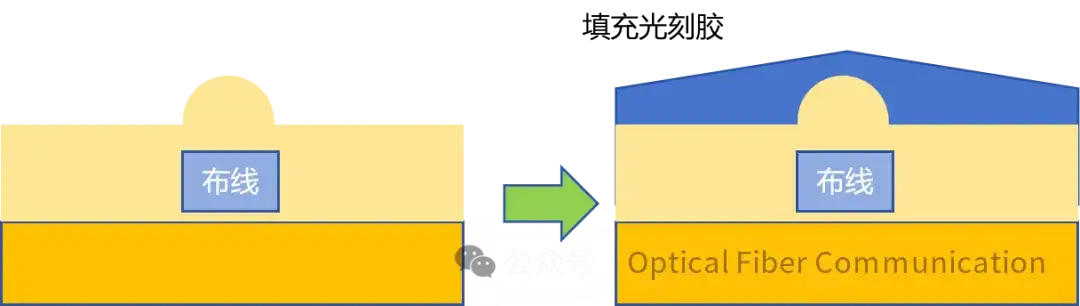

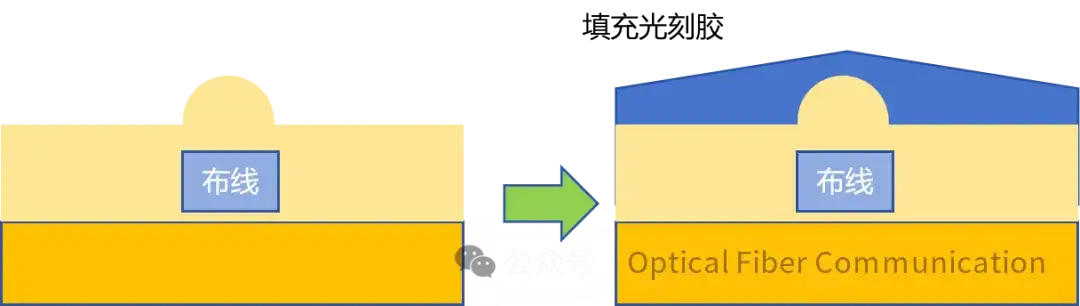

为了实现更多的功能和更高的性能,我们会在芯片上搭建起层层叠叠的线路。这就是我们常说的多层布线技术。

但与此同时,它也带来了一个挑战:每增加一层线路,就像在原本平滑的地面上堆砌砖块,使得芯片表面变得坑坑洼洼。这种不平整的表面不仅影响了电流的传输效率,还可能引发一系列缺陷和故障,对后续的制造工艺构成了不小的威胁。

[……]

经公众号Optical Fiber Communication同意发布。

在 Intel 实验室,制造线的统一着装被称之为 “兔子服(Bunny Suit)”。如果加上两只毛茸茸的耳朵就更像了。

这里的兔子服指的就是“洁净室套装”,是洁净室内工作人员的标准装备。在半导体、纳米技术生产线上,工程师和技术人员都需身着这类一体式工作服,以确保工作环境的洁净度。这类防护服的设计旨在全面覆盖[……]

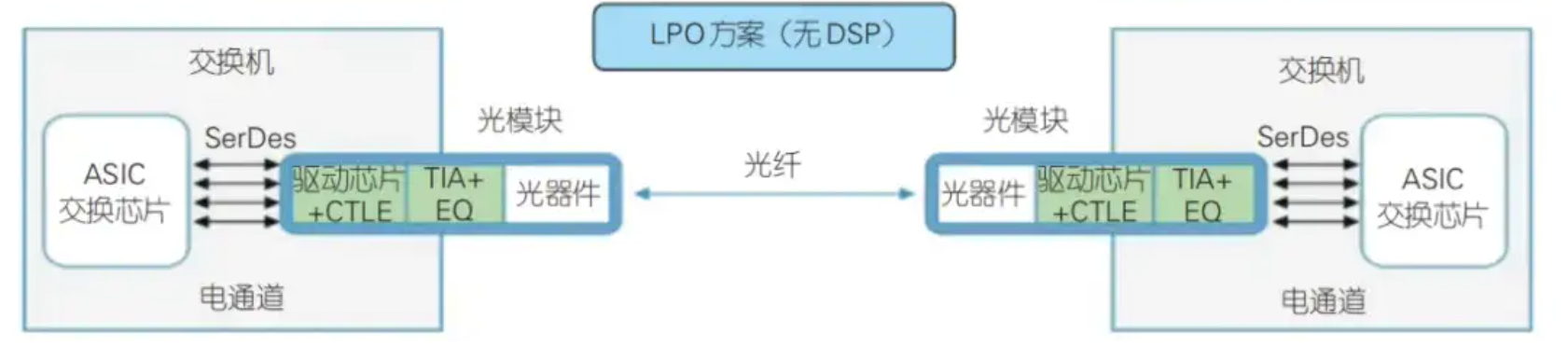

问:什么是线性可插拔光学器件(LPO)?

答:LPO,英文Linear Pluggable Optics,中文即线性可插拔光学器件,是指一种利用低功耗可插拔模块的解决方案,该模块不包含 DSP 芯片。链路中端点到端点之间的信号路径被视为线性的,通过专业化实现低功耗。与带有 DSP 的传统可插拔模块一样,符合 LPO MSA 标准的链路可用于交换机和网卡等各种网络和计算设备。

问:L[……]

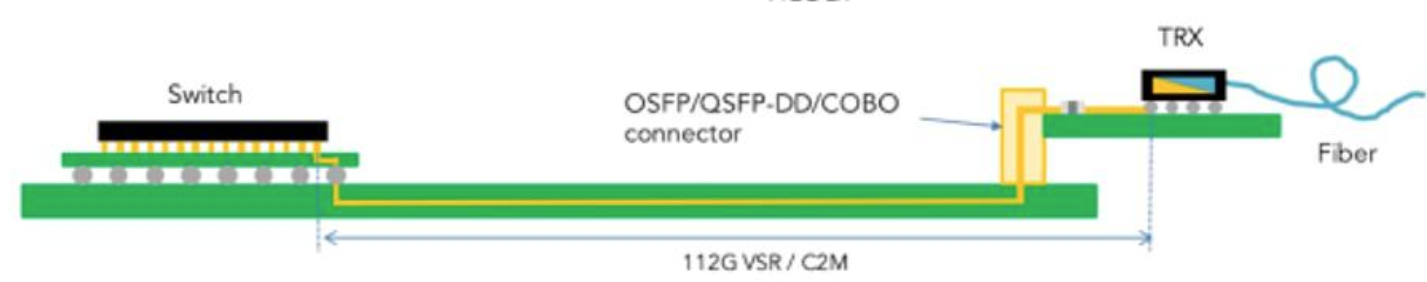

最近在读CPO和LPO相关资料,今天来简单聊聊,也算是学习总结。

传统的光模块是独立于交换芯片之外,通过铜缆或光纤与其他电子组件相连,这种方式在高速信号传输过程中容易产生较大的功耗和信号损耗。

另外,DCI等网络速率逐渐从400G发展到800G,甚至1.6T,不久的将来可达到3.2T。随着速率的提升,单个光模块的功耗也在直线上升,从而导致整机功耗大大增加。

图1-数据中心连接[……]

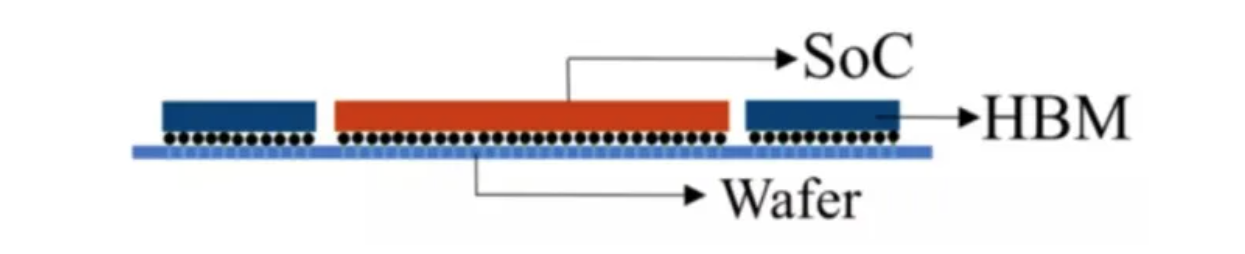

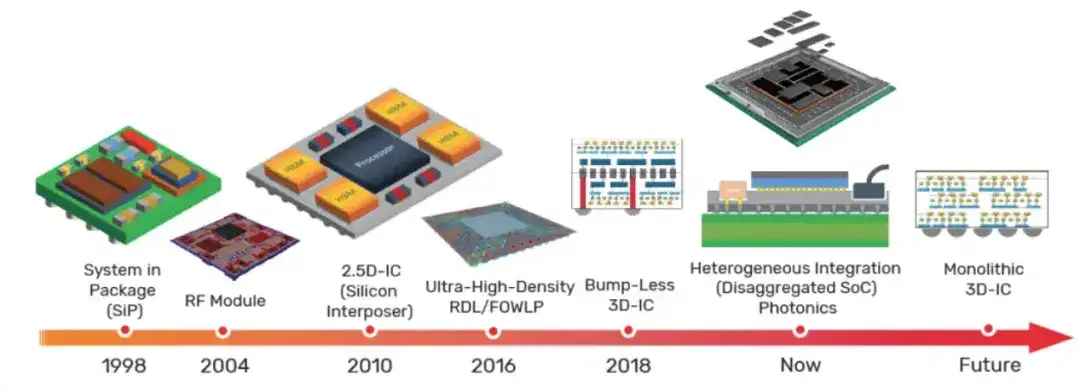

当前绝大多数芯片厂商走的都是SoC(片上系统)的路子。即从不同IP供应商购买软核IP或硬核IP,再结合自研模块集合成一个片上系统,然后以某个制造工艺节点生产出芯片。

但是,在超越摩尔定律的技术方向上,人们普遍认为小芯片(Chiplet)技术将是未来芯片设计的方向。这是一种搭积木造芯的模式,通过内部互联技术实现多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片。据我们了解英特尔等少数几家公[……]

荷兰的”贝多芬行动”和美国的”翻滚贝多芬计划“。

荷兰 | 贝多芬行动

说起现在荷兰的明星企业,那绝对是光刻机大佬ASML没跑了!这家伙赚钱能力可不是盖的,简直是荷兰的“小金库”,养活了不知多少荷兰人民的小心心。

可是最近,ASML似乎对荷兰国内的一些政策有些不满,竟然放出狠话,说要离家出走!这可把荷兰ZF吓得不轻,毕竟ASML一走,荷兰可就失去了这棵摇钱树,那日子可咋过[……]

什么是刻蚀

在半导体制造的奇妙世界里,有一种技术如同一位隐形的英雄,默默地将光刻胶上的精细图案精准地转移到下层材料上,它就是刻蚀技术。这项技术,就像一位精湛的雕刻家,用物理或化学的“刻刀”,在硅片表面雕刻出千变万化的图形。

想象一下,光刻胶层上承载着设计好的电路图案,它们就像待雕刻的玉石,等待着刻蚀技术的精细加工。

图-未经刻蚀的衬底

而刻蚀技术,就是那位能够将这些图案[……]

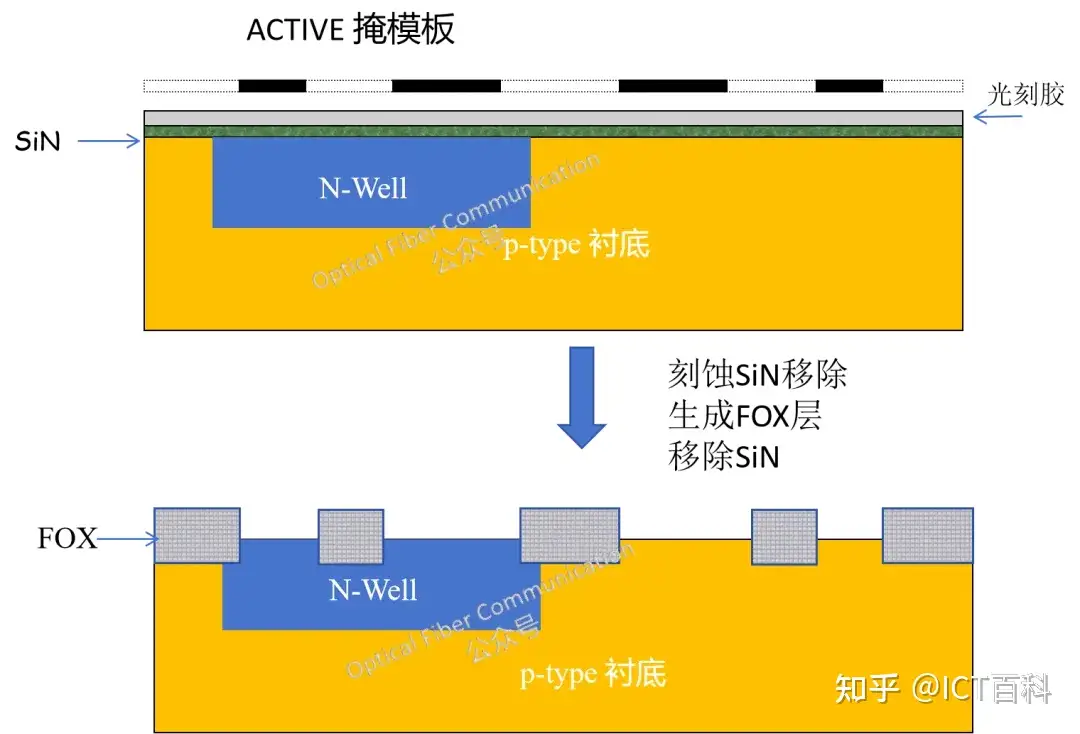

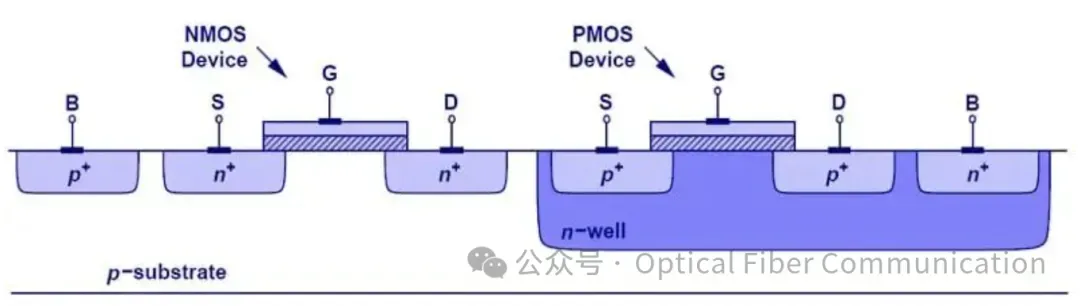

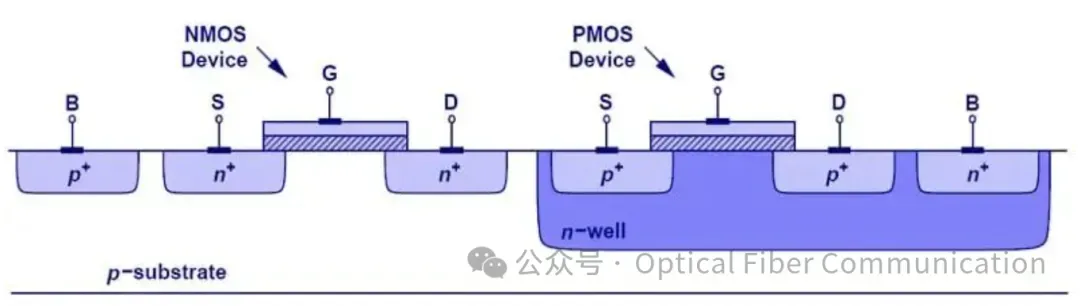

CMOS即Complementary MOSFET,由PMOS场效应管和NMOS场效应管以对称互补的形式组成,因此也叫互补型MOSFET。CMOS可以说是现代集成电路的基石。

在过去的20来年里,CMOS技术取得了重大进展。下面是COMS的演进,从双栅极、三栅极、π栅极、ω栅极到全栅极…..

图MOSFET的演进来看FinFET,因为通道是垂直的,长得像鳍,因此叫鳍状场效应[……]

什么是光刻?

光刻是集成电路(IC或芯片)生产中的重要工艺之一。简单地说,就是利用光掩模和光刻胶在基板上复制电路图案的过程。

硅片上涂有二氧化硅绝缘层和光刻胶。光刻胶在紫外光照射下很容易被显影剂溶解,经过溶解和蚀刻后,电路图案就会留在基板上。

光刻胶与树脂、溶剂和添加剂结合在一起。光刻胶的感光范围为200nm-500nm。因此,许多半导体实验室会采用黄光来阻挡500nm紫外波[……]

什么是ASIC芯片?

ASIC,全称为 Application Specific Integrated Circuit,中文名为专用集成电路芯片,顾名思义,是一种为了专门目的或者算法而设计的芯片。ASIC 芯片的架构并不固定,既有较为简单的网卡芯片,用于控制网络流量,满足防火墙需求等等,也有类似谷歌 TPU,昇腾 910B 一类的顶尖 AI 芯片。ASIC 并不代表简单,而是代表面向的需求,[……]

半导体激光器为什么需要窄线宽?

目前,随着网络流量的需求爆发式增长,光纤通信传输速率得到大幅提升,其中一种提升传输速率的方式就是通过更高更复杂的调制格式,这对激光器的线宽要求变得更高。

此外,在光谱学、计量学和生化传感等领域对激光器的线宽提出了更高的要求。例如,FMCW激光雷达的线宽必须足够小,从而保证在200 m以外反射回来的光也能与参考光相干。

图 FMCW激光雷达原理图[……]

硅外延层和衬底是半导体制造过程中的两个重要组成部分。衬底是半导体芯片制造的基础,主要由单晶硅材料制成。硅外延层是在衬底上加工生长的一层硅材料,其材料特性与衬底相同。二者在成份、结构和性质上都有所不同。

一、衬底

衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。衬底是晶圆(把晶圆切开,就可以得到一[……]

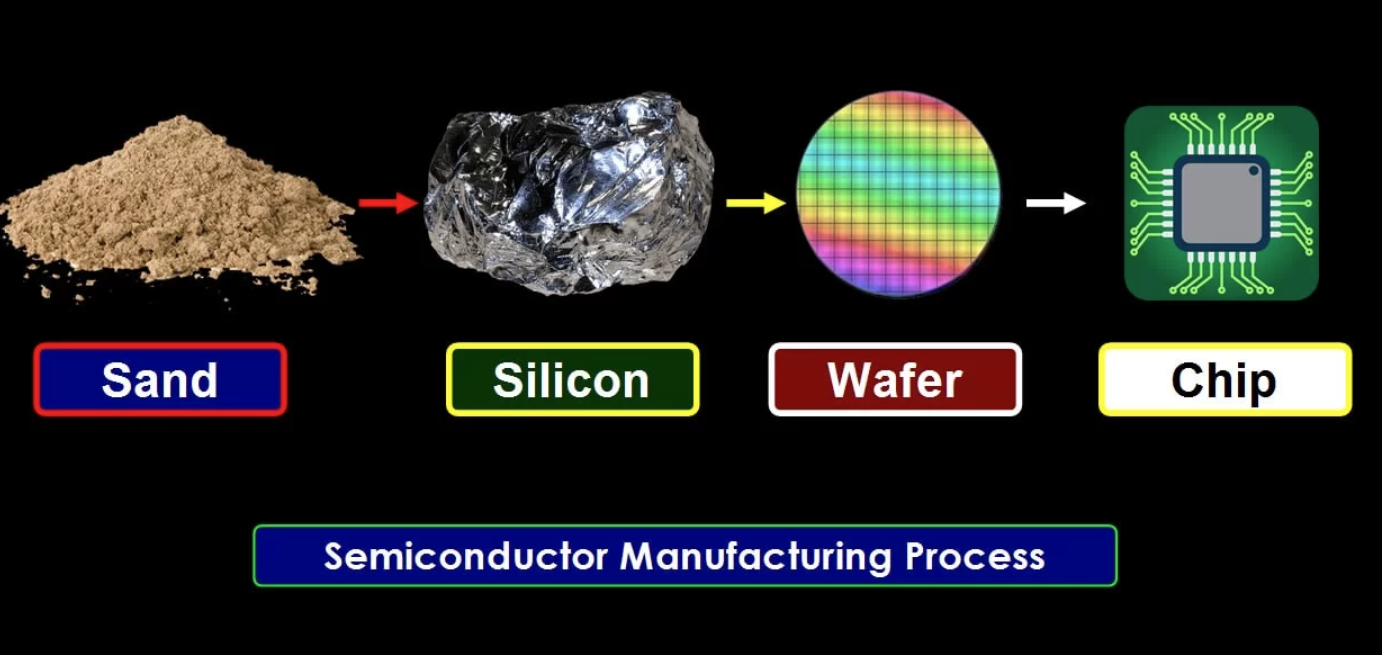

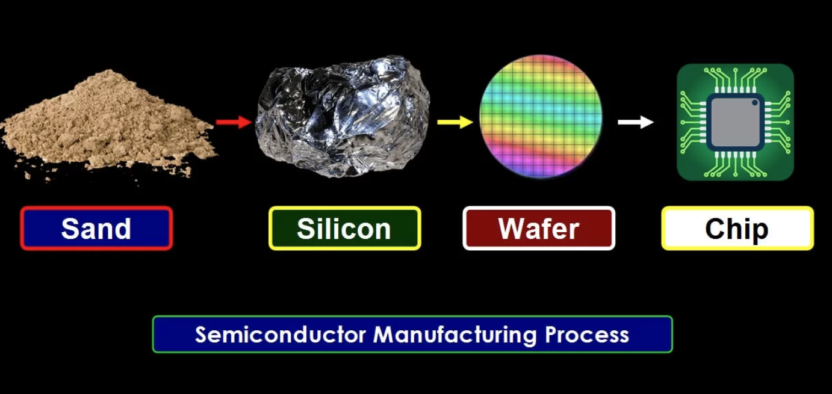

硅要变成半导体芯片,需要经过晶圆制造、氧化、光刻、蚀刻、沉积和离子注入、金属布线、EDS 和封装等几个复杂的过程。

让我们来详细了解一下这个重要的半导体制造过程。

现在让我们详细了解上述的所有步骤。

1. 硅晶圆制造–所有半导体的基础

半导体堆得又高又结实,形成了类似高层建筑的复杂结构。建筑从地基开始。同样,硅晶圆也是半导体的地基。

大多数硅片都是由从沙子中[……]

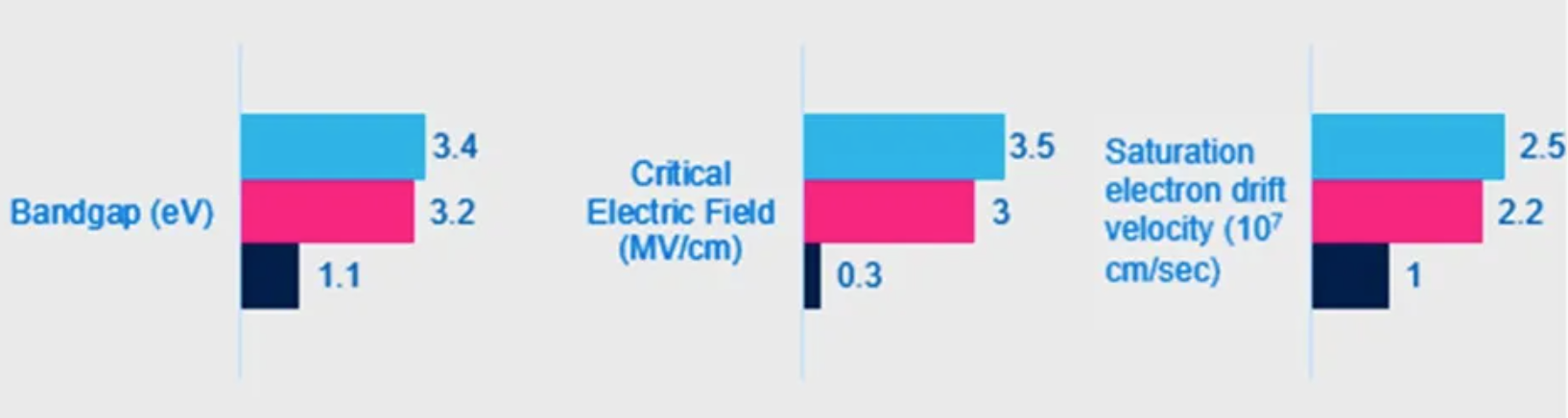

氮化镓和碳化硅同属于一类被称为宽禁带(wide-bandgap,WBG)半导体材料。价带的最高能量占用状态与导带的最低未占用状态之间的能量差称为带隙,以表示材料的电导率。通俗来讲,带隙所代表的能量差,即让一个半导体从绝缘到导电所需的最低能量。较大的带隙意味着需要更多的能量才能将价电子激发到导带。相反,当价带和导带像金属一样重叠时,电子可以很容易地在两个带之间跳跃,这意味着该材料被归类为导体。

[……]

干法刻蚀技术是一种在大气或真空条件下进行的刻蚀过程,通常使用气体中的离子或化学物质来去除材料表面的部分,通过掩膜和刻蚀参数的调控,可以实现各向异性及各向同性刻蚀的任意切换,从而形成所需的图案或结构。常见的干法刻蚀设备有反应离子刻蚀机(RIE)、电感耦合等离子体刻蚀机(ICP)、磁性中性线等离子体刻蚀机(NLD)、离子束刻蚀机(IBE),本文目的对各刻蚀设备的结构进行剖析,以及分析技术的优缺点。

[……]

主要内容:

⚫全球关键发展议题扫描

⚫前瞻全球与台湾半导体发展议题

⚫剖析全球与台湾半导体竞合议题

⚫全球与台湾半导体产业发展瞭望

⚫结论

下载过程中若有任何问题,请及时联系微信:TXBK2019

[……]

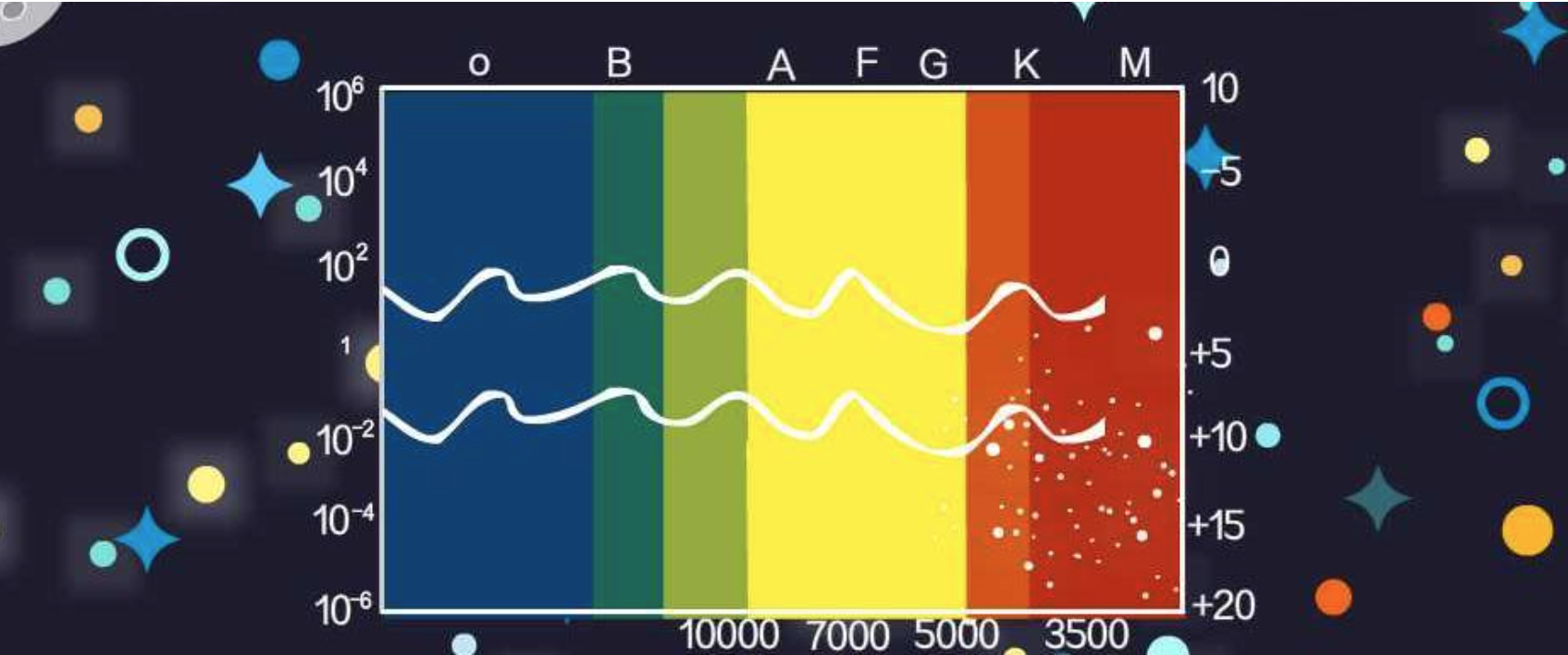

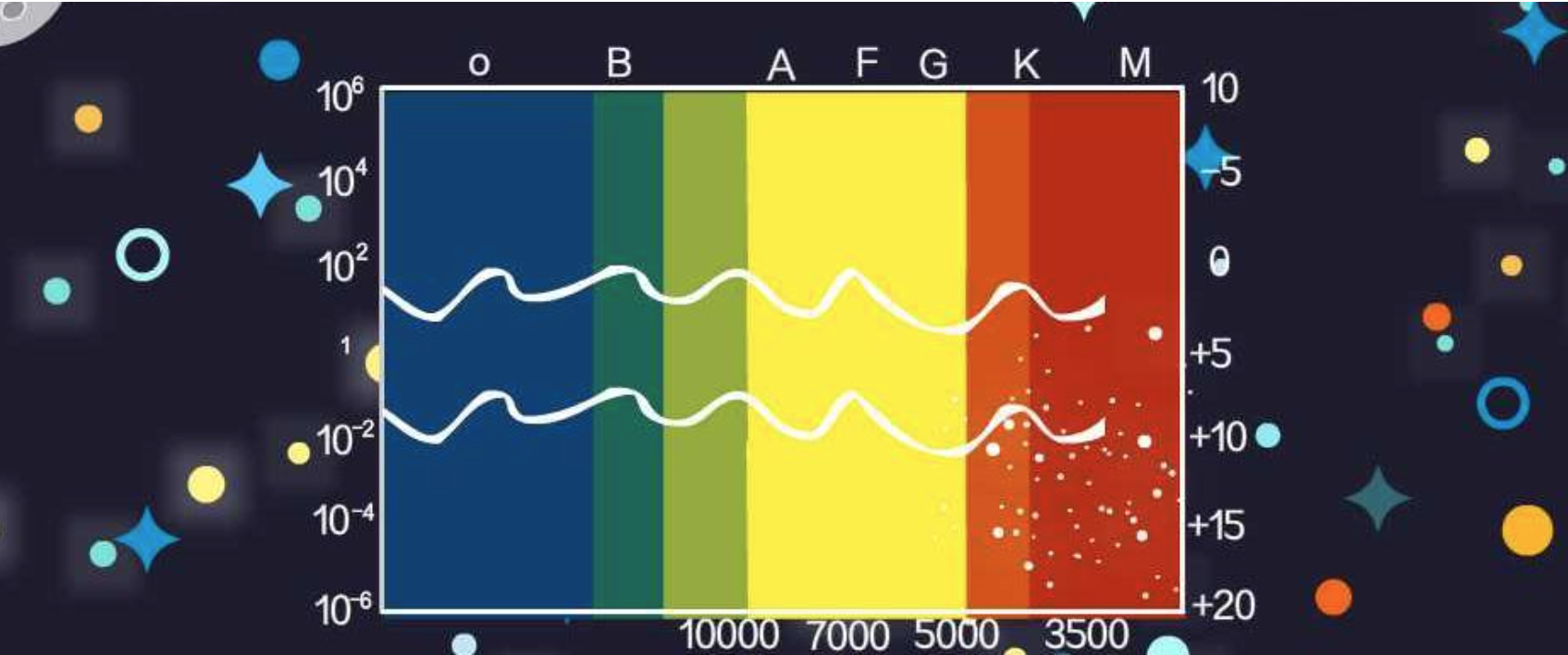

在光纤通信行业工作了很长时间后,我们理所当然地认为多模对应850nm,或850nm,910nm波长。单模对应1260-1650nm波长,尤其是1310nm波段附近和1550nm波段附近的波长。

嘿,有一天我们偶然知道有波长为1550nm的多模激光器,也有波长为1310nm的多模激光器。这是怎么发生的?事实上,850nm也可以制成单模激光器。在业内,单模指的是单横向模式,多模指的是多横向模式。[……]

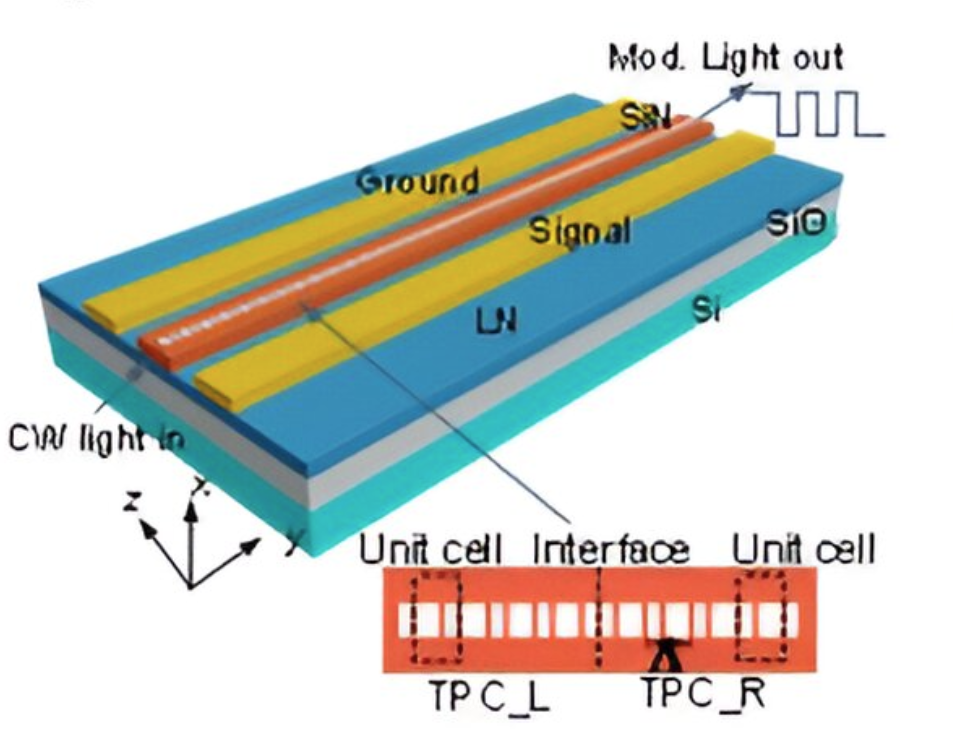

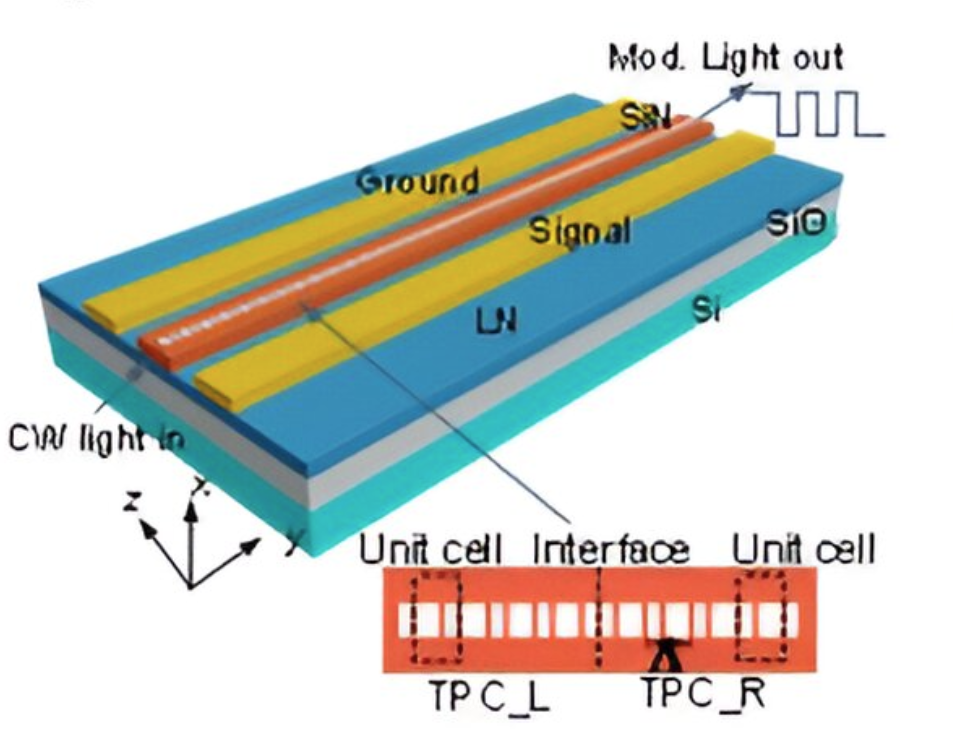

电光调制器将信号从电域转换到光域,是光通信、太赫兹无线通信、微波信号处理和量子技术的核心。下一代光电调制器需要高密度集成、紧凑的尺寸、大带宽和低功耗。现有的集成马赫-泽恩德干涉仪(MZI)或微栅器件很难实现这些要求。

由于拓扑光子学的独特特性,包括紧密的光学约束、光的稳健传输和对缺陷的免疫,具有拓扑界面态的集成铌酸锂(LN)波导有助于应对下一代电光调制器的挑战。

拓扑相变已被用于演示集[……]

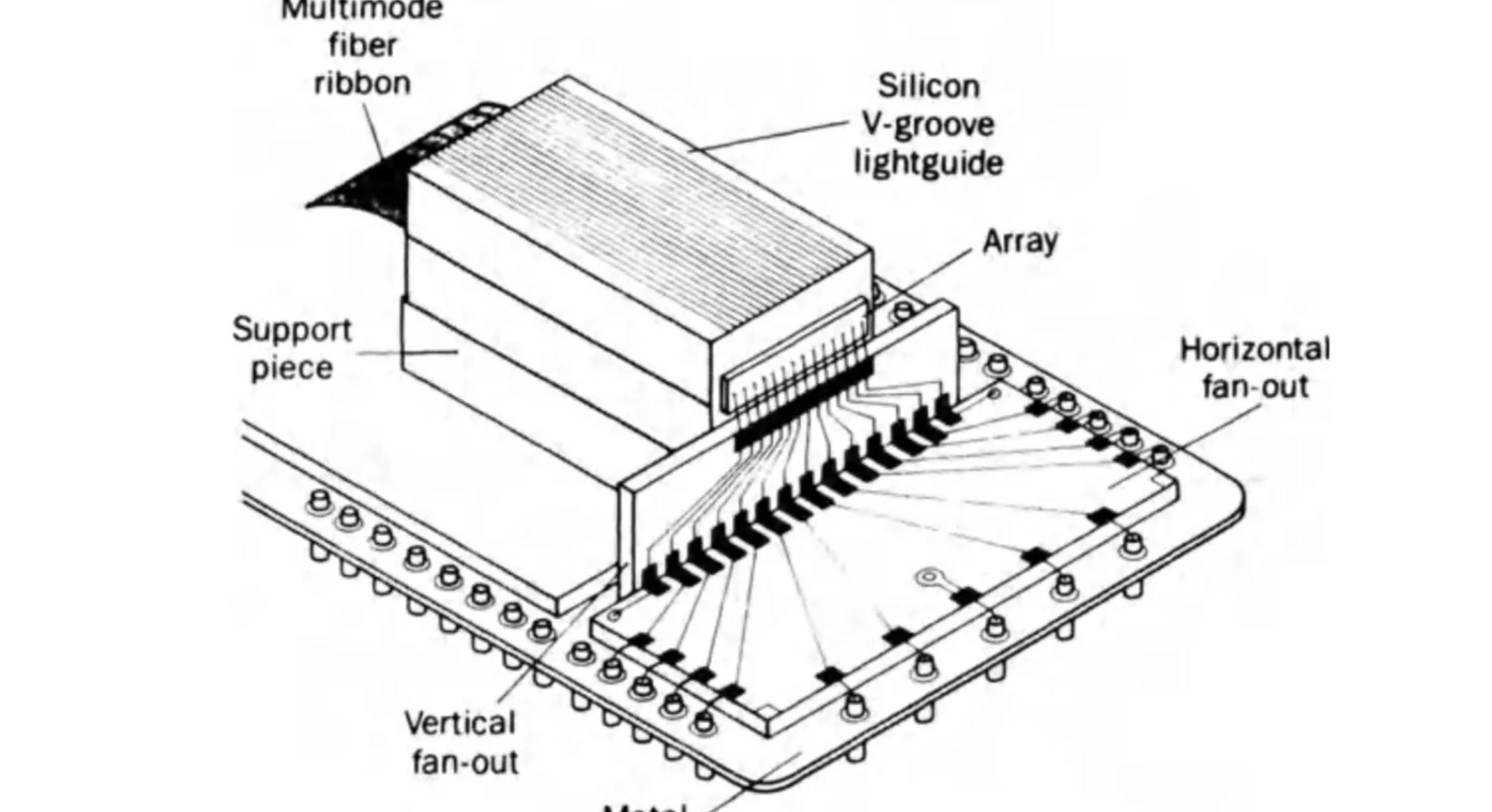

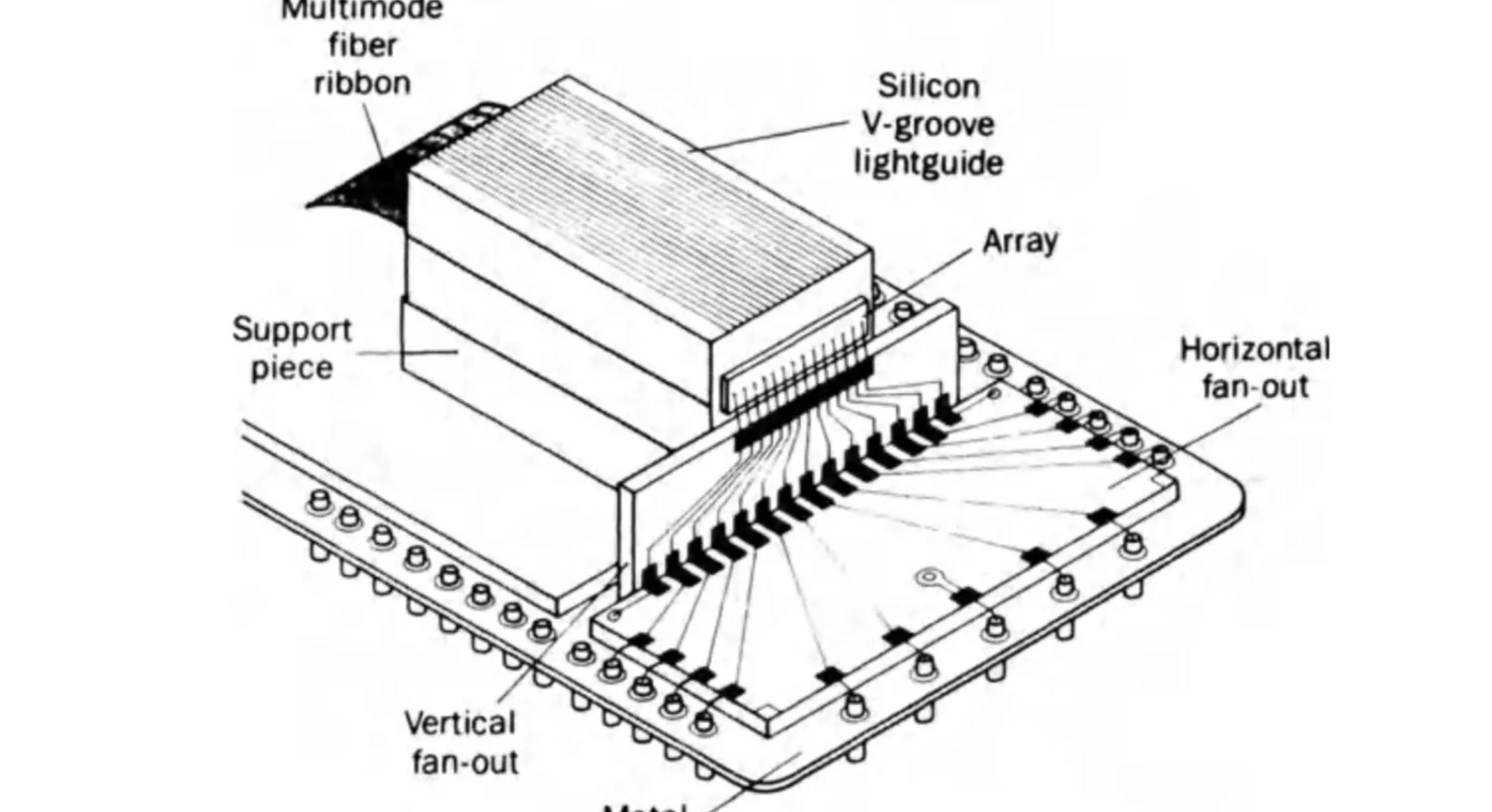

20 世纪 80 年代和 90 年代初,将半导体激光器和其他相关器件集成到单个芯片上的光学和电子集成技术取得了重大发展。

这些芯片可实现比单个器件更高水平的功能。例如,激光器和电子驱动电路已经集成,可作为简单的单片光波发射器。同样,光探测器也与基于场效应晶体管(FET)或异质结双极晶体管(HBT)的放大器电路集成在一起。这种集成器件可作为接收器的前端。

光电集成不仅是光子学领域的一项技[……]

在我们的社群有问到“减薄工艺与CMP”方面的问题。表面去年,CMP也有减薄的作用,但其实不太一样,另外还有一个磨削研磨的工艺,可能也会有所误解。下面我们放在一起来聊一聊。

为了更直观的展现这几个工艺的不同,我们先看看它们在制造流程中的位置,画了一个包含部分流程的示意图,如下。

图中的黄色底是磨削/研磨工艺,绿色背景的是CMP平坦化工艺,红色底的是减薄工艺。可以看出,在流程顺序上,它[……]

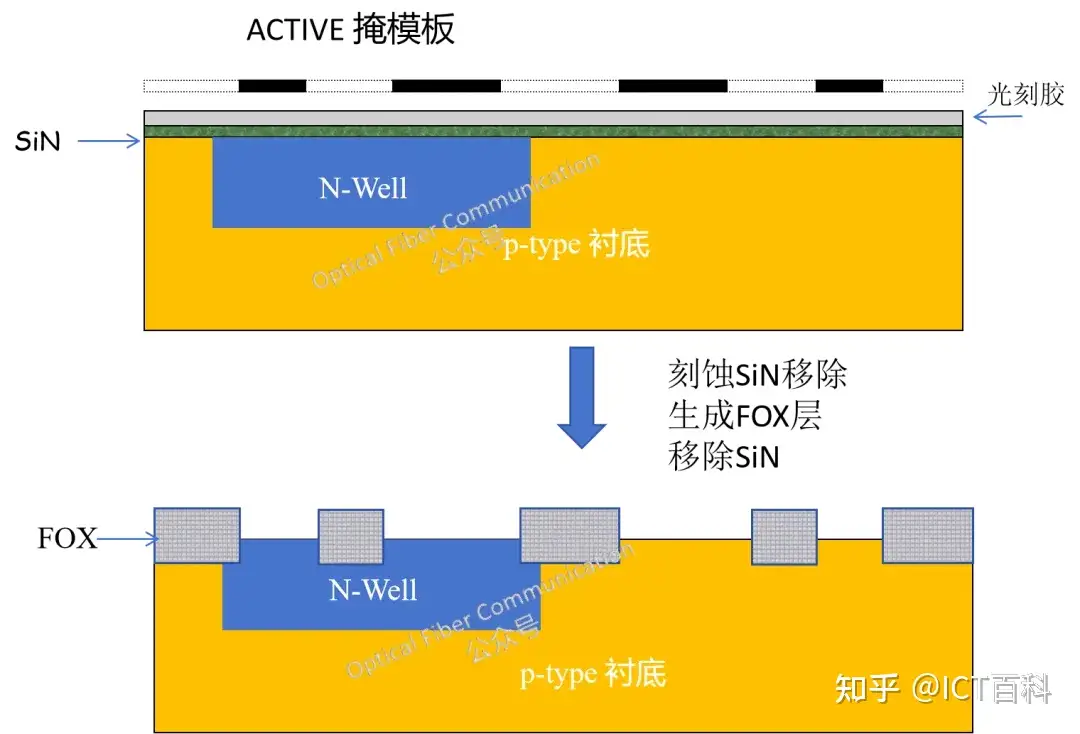

半导体领域,掩膜板相当于老式相机拍照用到的“底片”,光刻就在这个“底片”上,将上面的图形准确地转移到下面的光刻胶上。(底片这玩意儿可能很多90后00后没有接触过)。

用于制作掩膜板的材料,主要由高品质的石英玻璃基板和在表面沉积的遮光材料构成,其中遮光材料通常用的是铬(Cr)。选择铬膜是因为它的沉积与刻蚀相对比较容易,而且对光线完全不透明。

那么掩膜板需要覆盖光刻胶的所有位置吗?其实[……]

SMT(Surface Mount Technology),即表面贴装技术或表面组装技术,是直接将电子组件(如电阻、电容、集成电路等)贴装在 PCB 的表面上。它在电子组装阶段常见,同时在芯片贴装工艺上,SMT 也可以用于将封装后的芯片安装到 PCB 上。

图:SMT 贴装

与之对比的通孔技术 THT(Through-Hole Technology),则是比较传统的,它是将电子组件[……]

半导体的重要性就不细说了,大家可以想象到的日常生活中的所有电子产品都有使用到半导体器件。

其中,我们对这些产品最关心的一个共性指标就是:这货到底能用多久?

这个问题我们能否让用户帮我们检验?当然不能,除非是一锤子买卖。

为了产品在市场上不尴尬,就得从产品的可靠性说起了。也就是需要做芯片制造中三大测试之一的可靠性测试。

那什么是可靠性?引用某个规范中的一段话来说:[……]

经公众号Optical Fiber Communication同意发布。

为了实现更多的功能和更高的性能,我们会在芯片上搭建起层层叠叠的线路。这就是我们常说的多层布线技术。

但与此同时,它也带来了一个挑战:每增加一层线路,就像在原本平滑的地面上堆砌砖块,使得芯片表面变得坑坑洼洼。这种不平整的表面不仅影响了电流的传输效率,还可能引发一系列缺陷和故障,对后续的制造工艺构成了不小的威胁。

[……]

经公众号Optical Fiber Communication同意发布。

在 Intel 实验室,制造线的统一着装被称之为 “兔子服(Bunny Suit)”。如果加上两只毛茸茸的耳朵就更像了。

这里的兔子服指的就是“洁净室套装”,是洁净室内工作人员的标准装备。在半导体、纳米技术生产线上,工程师和技术人员都需身着这类一体式工作服,以确保工作环境的洁净度。这类防护服的设计旨在全面覆盖[……]

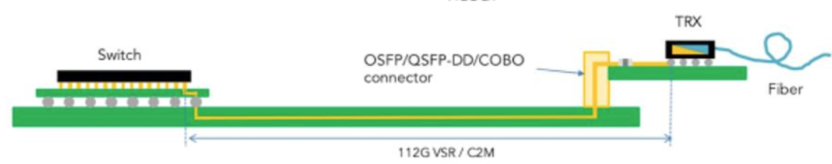

问:什么是线性可插拔光学器件(LPO)?

答:LPO,英文Linear Pluggable Optics,中文即线性可插拔光学器件,是指一种利用低功耗可插拔模块的解决方案,该模块不包含 DSP 芯片。链路中端点到端点之间的信号路径被视为线性的,通过专业化实现低功耗。与带有 DSP 的传统可插拔模块一样,符合 LPO MSA 标准的链路可用于交换机和网卡等各种网络和计算设备。

问:L[……]

最近在读CPO和LPO相关资料,今天来简单聊聊,也算是学习总结。

传统的光模块是独立于交换芯片之外,通过铜缆或光纤与其他电子组件相连,这种方式在高速信号传输过程中容易产生较大的功耗和信号损耗。

另外,DCI等网络速率逐渐从400G发展到800G,甚至1.6T,不久的将来可达到3.2T。随着速率的提升,单个光模块的功耗也在直线上升,从而导致整机功耗大大增加。

图1-数据中心连接[……]

当前绝大多数芯片厂商走的都是SoC(片上系统)的路子。即从不同IP供应商购买软核IP或硬核IP,再结合自研模块集合成一个片上系统,然后以某个制造工艺节点生产出芯片。

但是,在超越摩尔定律的技术方向上,人们普遍认为小芯片(Chiplet)技术将是未来芯片设计的方向。这是一种搭积木造芯的模式,通过内部互联技术实现多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片。据我们了解英特尔等少数几家公[……]

荷兰的”贝多芬行动”和美国的”翻滚贝多芬计划“。

荷兰 | 贝多芬行动

说起现在荷兰的明星企业,那绝对是光刻机大佬ASML没跑了!这家伙赚钱能力可不是盖的,简直是荷兰的“小金库”,养活了不知多少荷兰人民的小心心。

可是最近,ASML似乎对荷兰国内的一些政策有些不满,竟然放出狠话,说要离家出走!这可把荷兰ZF吓得不轻,毕竟ASML一走,荷兰可就失去了这棵摇钱树,那日子可咋过[……]

什么是刻蚀

在半导体制造的奇妙世界里,有一种技术如同一位隐形的英雄,默默地将光刻胶上的精细图案精准地转移到下层材料上,它就是刻蚀技术。这项技术,就像一位精湛的雕刻家,用物理或化学的“刻刀”,在硅片表面雕刻出千变万化的图形。

想象一下,光刻胶层上承载着设计好的电路图案,它们就像待雕刻的玉石,等待着刻蚀技术的精细加工。

图-未经刻蚀的衬底

而刻蚀技术,就是那位能够将这些图案[……]

CMOS即Complementary MOSFET,由PMOS场效应管和NMOS场效应管以对称互补的形式组成,因此也叫互补型MOSFET。CMOS可以说是现代集成电路的基石。

在过去的20来年里,CMOS技术取得了重大进展。下面是COMS的演进,从双栅极、三栅极、π栅极、ω栅极到全栅极…..

图MOSFET的演进来看FinFET,因为通道是垂直的,长得像鳍,因此叫鳍状场效应[……]

什么是光刻?

光刻是集成电路(IC或芯片)生产中的重要工艺之一。简单地说,就是利用光掩模和光刻胶在基板上复制电路图案的过程。

硅片上涂有二氧化硅绝缘层和光刻胶。光刻胶在紫外光照射下很容易被显影剂溶解,经过溶解和蚀刻后,电路图案就会留在基板上。

光刻胶与树脂、溶剂和添加剂结合在一起。光刻胶的感光范围为200nm-500nm。因此,许多半导体实验室会采用黄光来阻挡500nm紫外波[……]

什么是ASIC芯片?

ASIC,全称为 Application Specific Integrated Circuit,中文名为专用集成电路芯片,顾名思义,是一种为了专门目的或者算法而设计的芯片。ASIC 芯片的架构并不固定,既有较为简单的网卡芯片,用于控制网络流量,满足防火墙需求等等,也有类似谷歌 TPU,昇腾 910B 一类的顶尖 AI 芯片。ASIC 并不代表简单,而是代表面向的需求,[……]

半导体激光器为什么需要窄线宽?

目前,随着网络流量的需求爆发式增长,光纤通信传输速率得到大幅提升,其中一种提升传输速率的方式就是通过更高更复杂的调制格式,这对激光器的线宽要求变得更高。

此外,在光谱学、计量学和生化传感等领域对激光器的线宽提出了更高的要求。例如,FMCW激光雷达的线宽必须足够小,从而保证在200 m以外反射回来的光也能与参考光相干。

图 FMCW激光雷达原理图[……]

硅外延层和衬底是半导体制造过程中的两个重要组成部分。衬底是半导体芯片制造的基础,主要由单晶硅材料制成。硅外延层是在衬底上加工生长的一层硅材料,其材料特性与衬底相同。二者在成份、结构和性质上都有所不同。

一、衬底

衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。衬底是晶圆(把晶圆切开,就可以得到一[……]

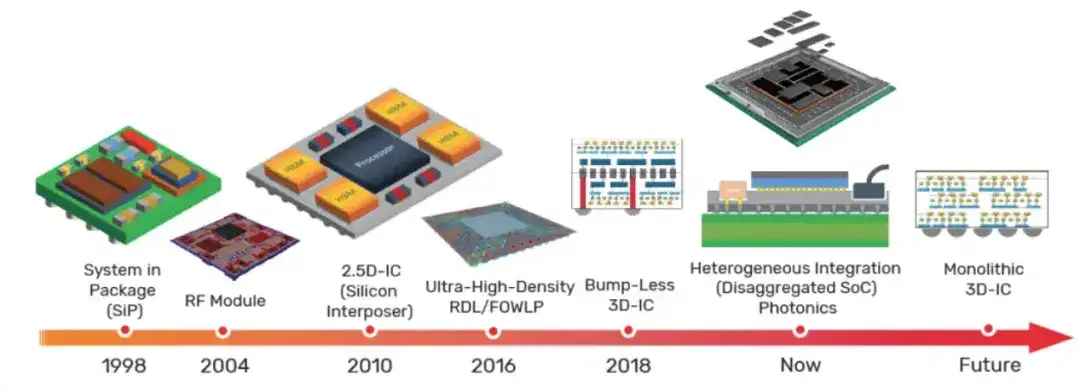

在以人工智能、高性能计算为代表的新需求驱动下,先进封装应运而生,发展趋势是小型化、高集成度,历经直插型封装、表面贴装、面积阵列封装、2.5D/3D封装和异构集成四个发展阶段。

先进封装开辟了 More-than-Moore的集成电路发展路线,能够在不缩小制程节点的背景下,仅通过改进封装方式就能提升芯片性能,还能够打破“存储墙”和“面积墙”。

先进封装也称为高密度封装,具有引脚数量较多、[……]

硅要变成半导体芯片,需要经过晶圆制造、氧化、光刻、蚀刻、沉积和离子注入、金属布线、EDS 和封装等几个复杂的过程。

让我们来详细了解一下这个重要的半导体制造过程。

现在让我们详细了解上述的所有步骤。

1. 硅晶圆制造–所有半导体的基础

半导体堆得又高又结实,形成了类似高层建筑的复杂结构。建筑从地基开始。同样,硅晶圆也是半导体的地基。

大多数硅片都是由从沙子中[……]

氮化镓和碳化硅同属于一类被称为宽禁带(wide-bandgap,WBG)半导体材料。价带的最高能量占用状态与导带的最低未占用状态之间的能量差称为带隙,以表示材料的电导率。通俗来讲,带隙所代表的能量差,即让一个半导体从绝缘到导电所需的最低能量。较大的带隙意味着需要更多的能量才能将价电子激发到导带。相反,当价带和导带像金属一样重叠时,电子可以很容易地在两个带之间跳跃,这意味着该材料被归类为导体。

[……]

干法刻蚀技术是一种在大气或真空条件下进行的刻蚀过程,通常使用气体中的离子或化学物质来去除材料表面的部分,通过掩膜和刻蚀参数的调控,可以实现各向异性及各向同性刻蚀的任意切换,从而形成所需的图案或结构。常见的干法刻蚀设备有反应离子刻蚀机(RIE)、电感耦合等离子体刻蚀机(ICP)、磁性中性线等离子体刻蚀机(NLD)、离子束刻蚀机(IBE),本文目的对各刻蚀设备的结构进行剖析,以及分析技术的优缺点。

[……]

主要内容:

⚫全球关键发展议题扫描

⚫前瞻全球与台湾半导体发展议题

⚫剖析全球与台湾半导体竞合议题

⚫全球与台湾半导体产业发展瞭望

⚫结论

下载过程中若有任何问题,请及时联系微信:TXBK2019

[……]

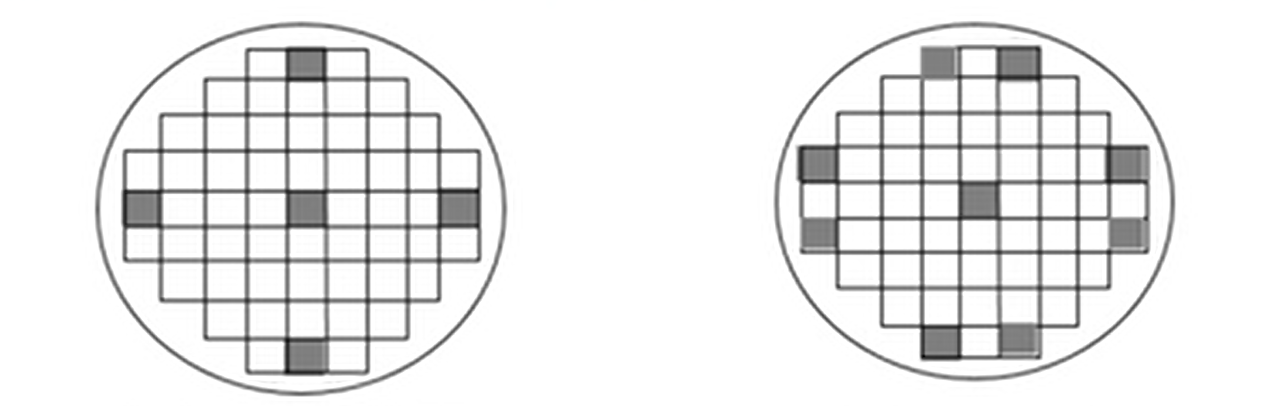

在光纤通信行业工作了很长时间后,我们理所当然地认为多模对应850nm,或850nm,910nm波长。单模对应1260-1650nm波长,尤其是1310nm波段附近和1550nm波段附近的波长。

嘿,有一天我们偶然知道有波长为1550nm的多模激光器,也有波长为1310nm的多模激光器。这是怎么发生的?事实上,850nm也可以制成单模激光器。在业内,单模指的是单横向模式,多模指的是多横向模式。[……]

电光调制器将信号从电域转换到光域,是光通信、太赫兹无线通信、微波信号处理和量子技术的核心。下一代光电调制器需要高密度集成、紧凑的尺寸、大带宽和低功耗。现有的集成马赫-泽恩德干涉仪(MZI)或微栅器件很难实现这些要求。

由于拓扑光子学的独特特性,包括紧密的光学约束、光的稳健传输和对缺陷的免疫,具有拓扑界面态的集成铌酸锂(LN)波导有助于应对下一代电光调制器的挑战。

拓扑相变已被用于演示集[……]

20 世纪 80 年代和 90 年代初,将半导体激光器和其他相关器件集成到单个芯片上的光学和电子集成技术取得了重大发展。

这些芯片可实现比单个器件更高水平的功能。例如,激光器和电子驱动电路已经集成,可作为简单的单片光波发射器。同样,光探测器也与基于场效应晶体管(FET)或异质结双极晶体管(HBT)的放大器电路集成在一起。这种集成器件可作为接收器的前端。

光电集成不仅是光子学领域的一项技[……]

EUV光刻胶是半导体制造工艺中使用的光敏材料,特别是在先进的光刻技术中。这些材料必须能够承受高能EUV光子,并提供高分辨率的图案化能力。开发EUV光刻胶材料的一些挑战是,它们需要对短波长高度敏感,实现高分辨率对于在3nm下生产复杂和小规模的图案至关重要,最大限度地减少线边缘粗糙度,并且除气(污染)给制造商带来了维持生产的问题。

这些创新材料通常被归类为化学放大光刻胶 (CAR)、非化学放[……]