半导体芯片的集成度越来越高,密度也越来越大。这直接带来一个变化:芯片上需要的引脚端子数量也跟着大幅增加。

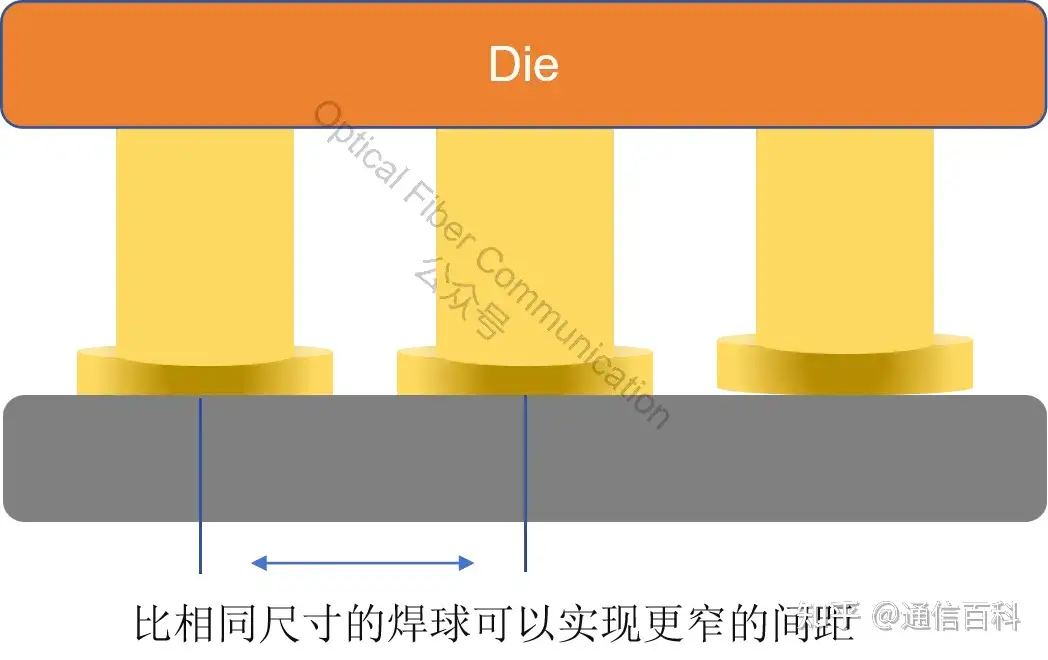

为了跟上这个趋势,同时应对越来越小的引脚间距,行业里的主流方案是用Cu Pillar(铜柱)来替代传统的C4焊锡球,以实现作为芯片与基板之间的互连。

在我们昨天的文章“

提到华为海思在其7.2T Hi-ONE硅光引擎中也使用了Cu Pillar技术。

我们先来说说什么是焊锡球,也就是C4,不是C4炸药哈。

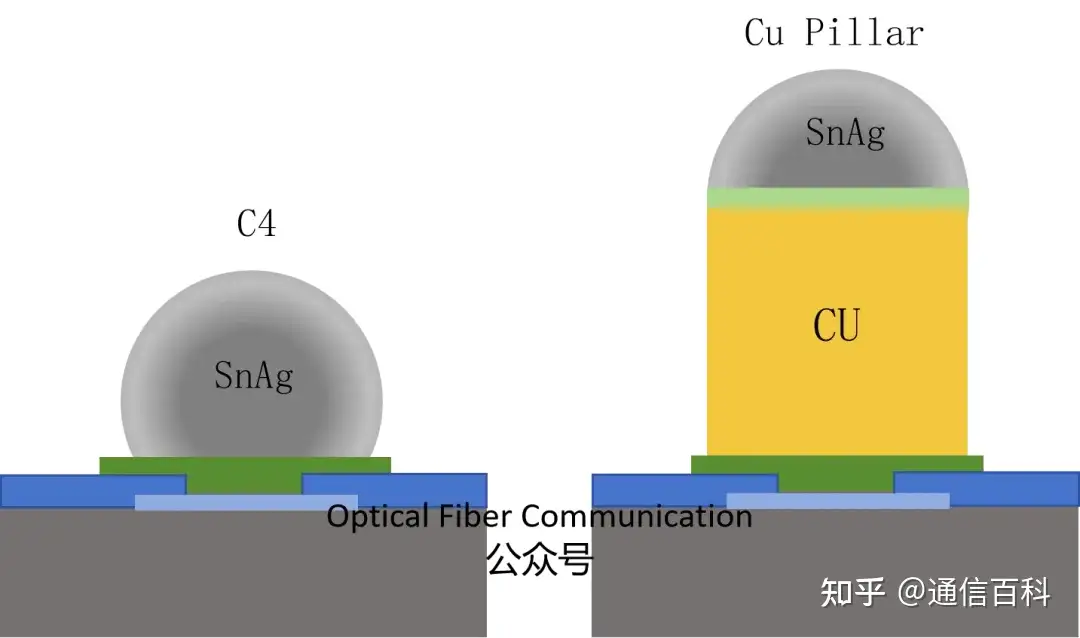

这里的C4,全称是 Controlled Collapse Chip Connection,翻译过来就是 “可控坍塌芯片连接技术”。

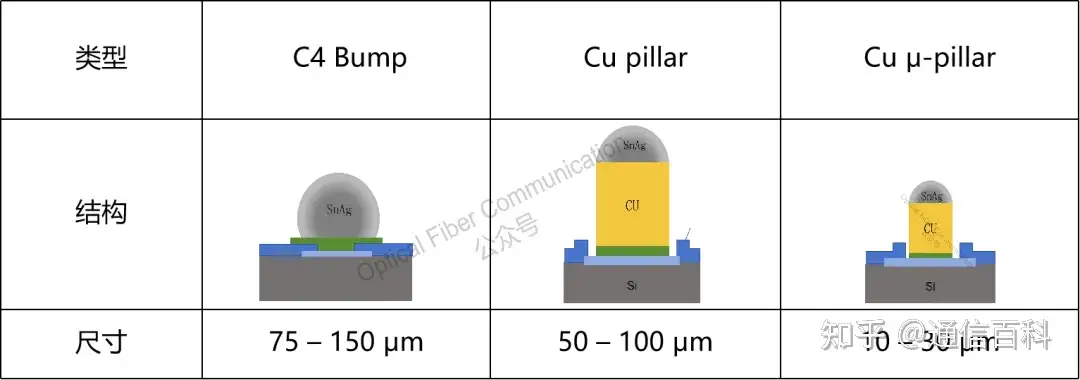

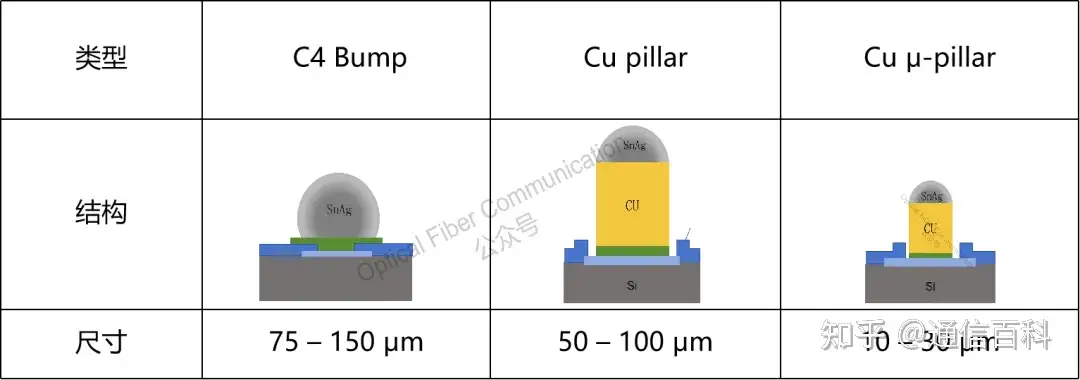

C4凸块的直径大约在75~150μm左右。在C4工艺中,经过回流焊熔化再凝固后,它的形状不完全是完美的球体,而更像一个圆顶状或蘑菇状的凸块。

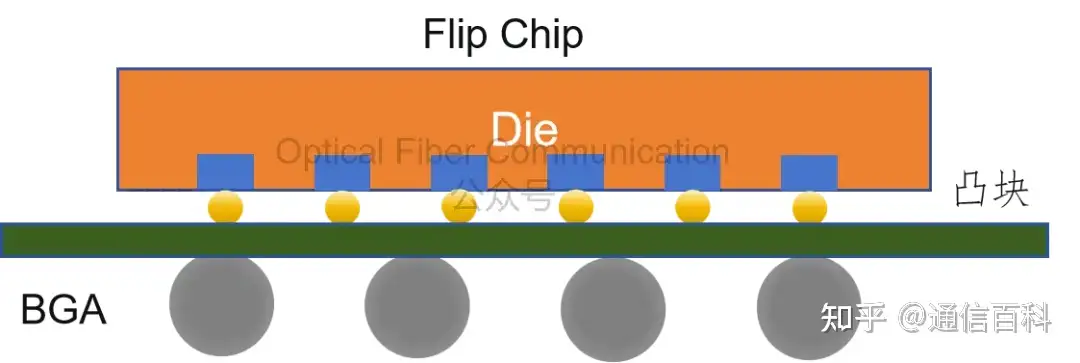

注意:在FC倒装芯片封装中,C4凸块用于连接芯片与封装基板,BGA焊球则用于连接封装基板与外部电路板。

除了在内部连接上取代C4,Cu Pillar的应用范围也在不断扩大。Cu Pillar技术正从芯片级向板级延伸,比如说日月光、Amkor 等厂商在推动 Cu Pillar 在FC-BGA中的应用。

那什么是Cu Pillar?

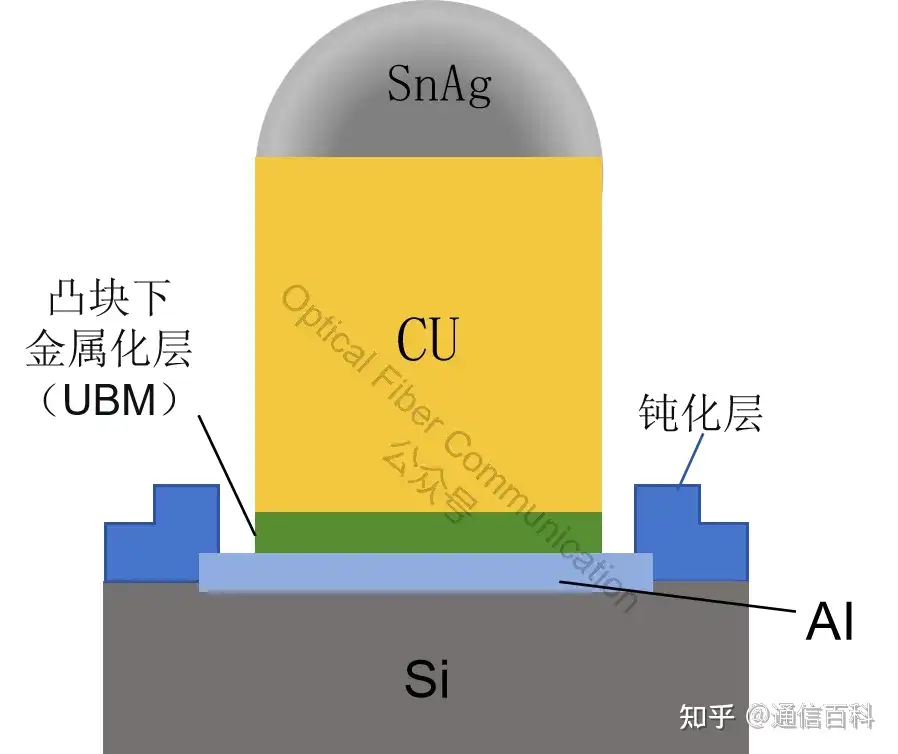

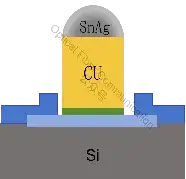

直译过来就是铜柱凸块,也叫C2,Chip Connection。它是一种利用铜柱接合替代传统引线键合,实现芯片与基板之间电气互联的先进制造技术。

Cu Pillar 的直径通常在几十μm到100μm左右。由于铜在回流焊过程中不会熔化,因此不会发生坍塌,能够维持非常稳定的互连高度。

目前,它已广泛应用于高密度倒装芯片封装中。

但随着先进封装不断向3D堆叠和异构集成方向发展,对互连密度的要求也达到了前所未有的高度。

此时,Cu Pillar技术就必须进一步演进到μ-bumps,对应的Cu μ-Pillar,即微铜柱,其直径进一步缩小到10~30µm 之间。

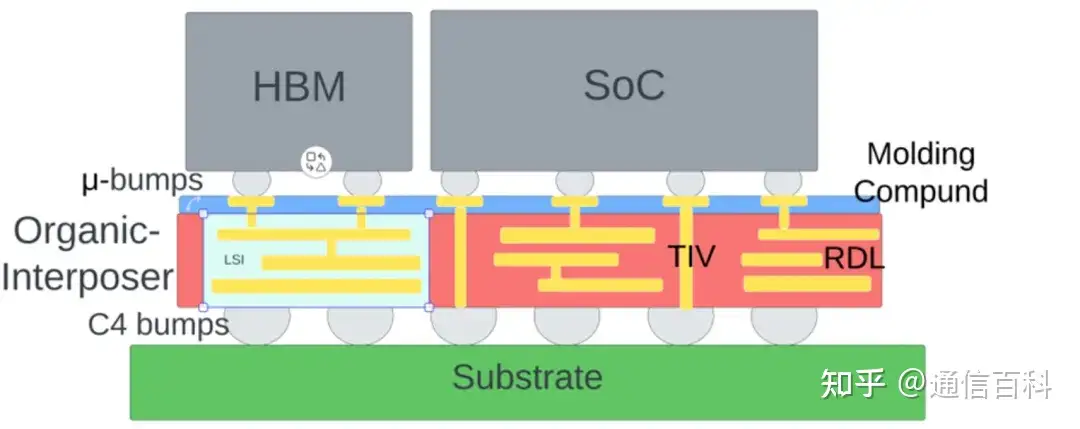

这种结构能够适应极高密度的封装需求,比如2.5D/3D IC集成、HBM堆叠等场景。在CoWoS几中类型中都有相关μ-bumps的应用。

比如说CoWoS-R封装:

通常来说,在最高端的3D IC和2.5D CoWoS封装中,当我们提到“μ-bumps”时,指代的往往就是“Cu μ-Pillar”这种结构。

我们用一张表来做个总结:

华为海思的Hi-ONE硅光引擎中,片上集成了超过2000个器件。从集成密度和技术趋势来判断,我们推测它采用的应该是更先进的 Cu μ-Pillar 技术。

感谢阅读!