若您对半导体/芯片/光器件模块/光纤通信等感兴趣

欢迎关注我们!

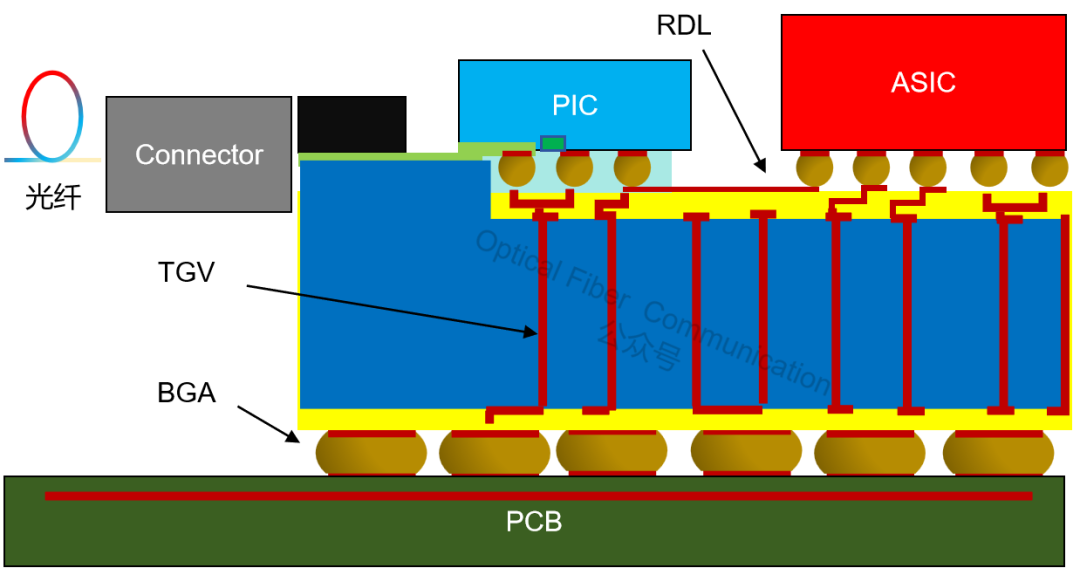

现在行业里发展出了多种先进封装,比如 FO(扇出型)、2D、2.5D,还有 3D 集成。这些技术都用到了不少关键工艺,比如 RDL、基于硅或玻璃的 Interposer(中介板)、TSV(硅通孔)和TGV(玻璃通孔)等等。

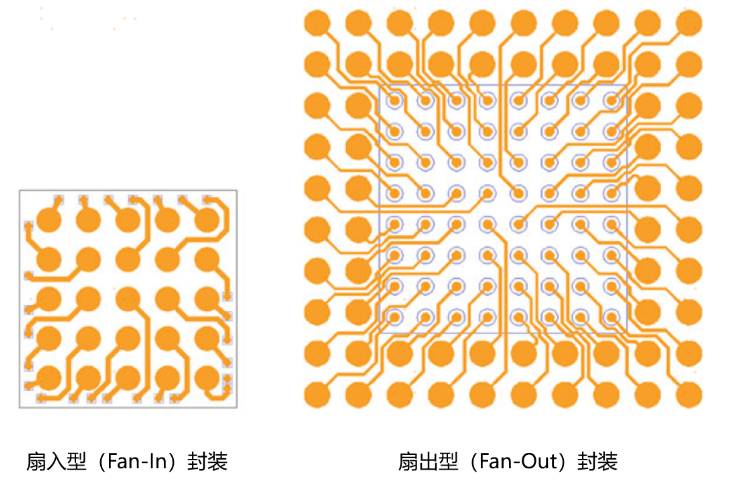

先说说 FO 扇出型封装。它的特点是把芯片的 I/O 接口从一个小小区域,”扇出”延伸到整个封装的大面积上,形成外部的焊球阵列。

这样做最直接的好处就是,在封装尺寸保持小巧的同时,能提供比传统封装多得多的 I/O 数量。

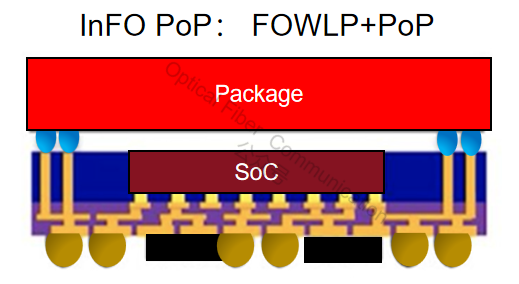

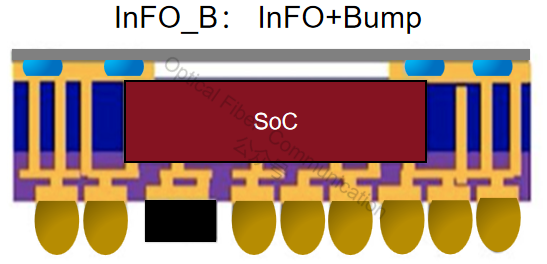

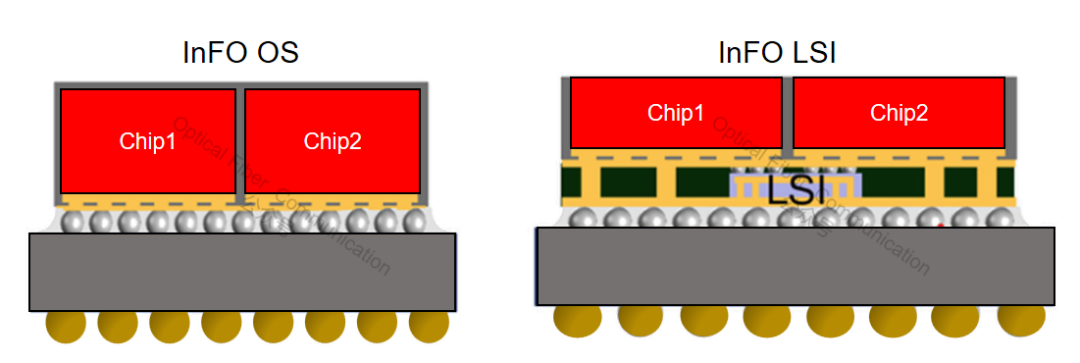

在这个领域,台积电的 InFO(集成扇出)技术是个典型代表。它还衍生出好几个变种,比如 InFO PoP、InFO B、InFO OS、InFO LSI 等等。

其中 InFO PoP 属于 3D 封装,是把 FOWLP(晶圆级扇出封装)技术和 PoP(堆叠封装)设计结合在了一起。

InFO B,也就是 InFO Bump,主要特点是在扇出结构里集成了凸起工艺。它跟传统 InFO 的主要区别就是在基板上增加了凸起 Bump。

InFO OS(InFO Open Substrate)和InFO LSI(InFO Logic System Integration)就不多说了,结构示意图如下:

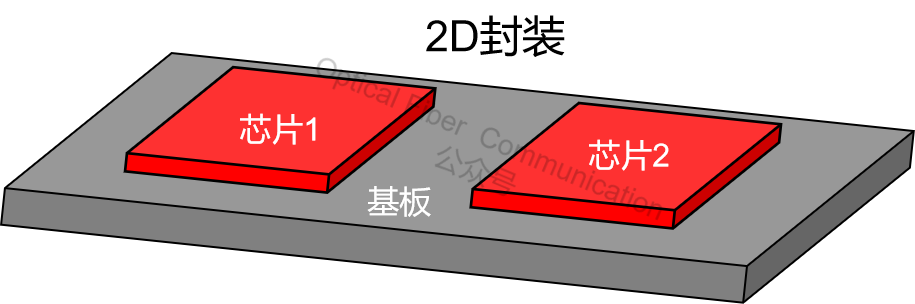

再来说说 2D 先进封装。顾名思义,就是把多个芯片或者晶粒以平面的方式排列在同一个基板上。

芯片之间通过细间距的互连技术连接,比如 Wire bonding、Flip-chip,或者是像Micro-bumps(微凸块)这类先进的键合技术。

扩展阅读:从C4, Cu Pillar 到 Cu μ-Pillar !

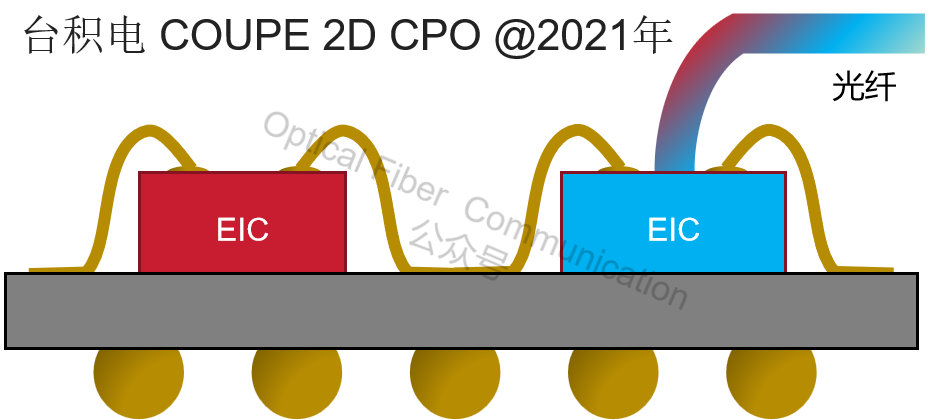

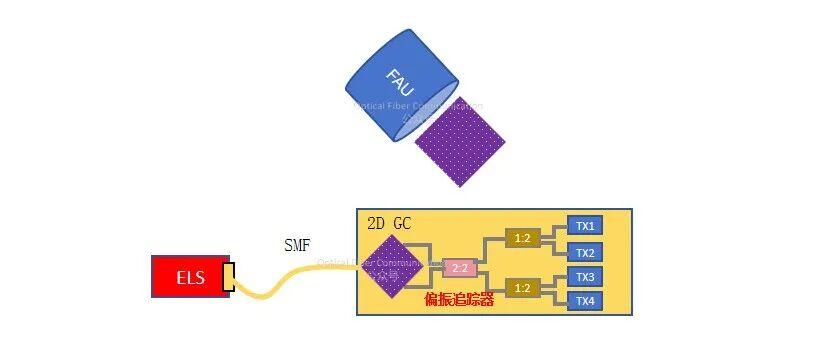

台积电基于 2D 先进封装技术,在 2021 年设计了一款 COUPE 2D 的 CPO 方案。其中 COUPE 平台采用 65nm 工艺,使用 12 寸晶圆。在这个方案里,EIC 和 PIC 通过 bonding 工艺集成在一起。

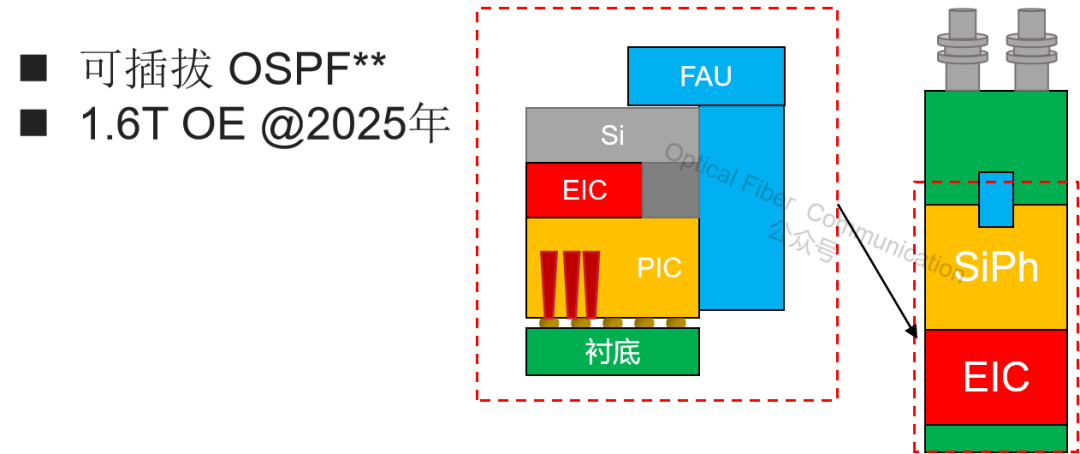

按照台积电今年 4 月份提供的路线图,他们计划在 2025 年实现可插拔光模块的 1.6T 光引擎,然后在 2026 年实现基于 CoWoS 封装技术的 6.4T CPO 光引擎。

接下来我们聊聊 2.5D 封装,它比 2D 多 “0.5” D,又进一步了。2.5D 是把所有芯片都并排放置在一个叫做 Interposer 层的”转接板”上。

Interposer 中介层其实是一块非常薄的硅片或者玻璃片,内部布满了高密度的线路,还有 TSV 或者 TGV。

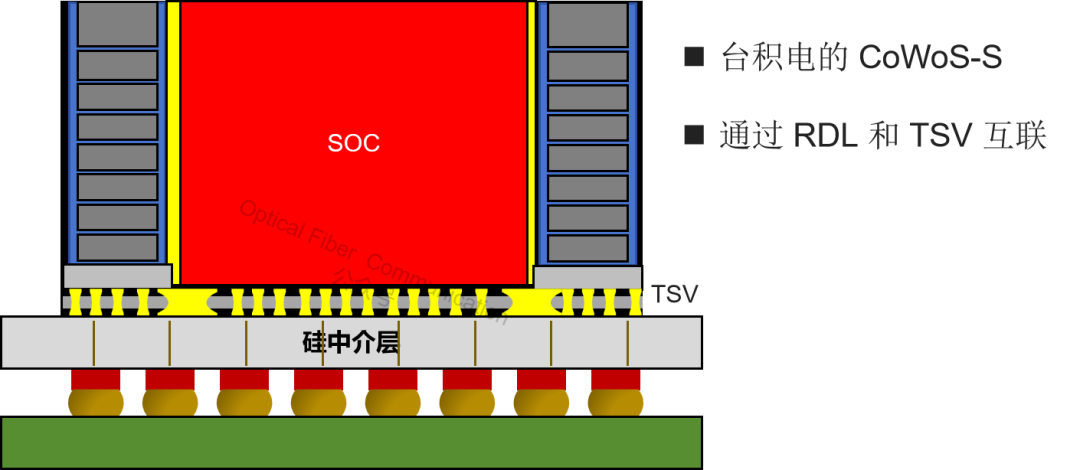

下面是台积电基于 Interposer 中介层的 2.5D 封装示意图。

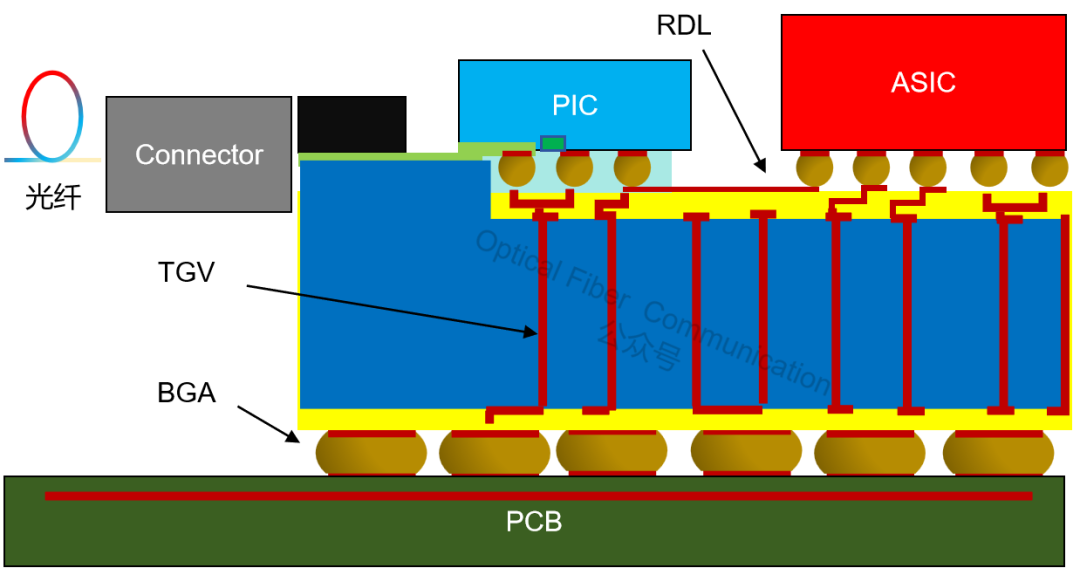

2.5D 封装在 CPO 应用上,也是通过硅或玻璃介质器将 PIC 与 EIC 互联,能够最大限度地缩短信号路径的长度和复杂度。

下面是康宁设计的玻璃基底 CPO 方案。

在这个方案里,芯片组通过细线电铜线连接,嵌入单面蚀刻腔内。PIC 则通过采用离子交换技术制造的玻璃波导与光纤连接。

为了进一步提升整个芯片系统的性能,又发展出了 3D 集成技术。它的主要特点就是把芯片垂直堆叠在单个封装中,通过 TSV、TGV 或微凸起进行垂直互联。

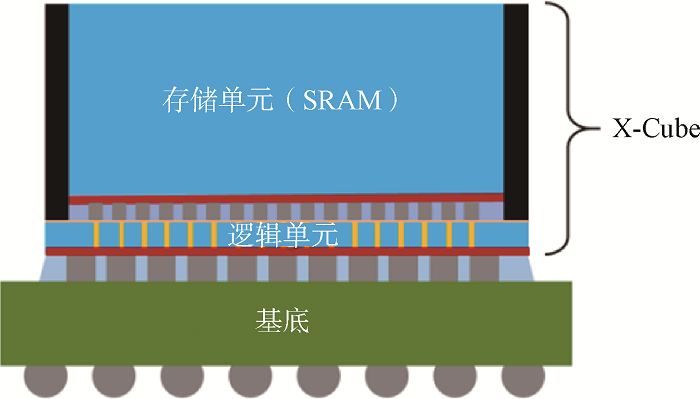

三星的 X-Cube 就是一个比较典型的例子,它将多个逻辑芯片和内存芯片集成到一个紧凑的封装中,采用了 3D 叠层和垂直互联的技术。

同样,3D 封装也应用在 CPO 中。激光器、光电探测器和调制器等光学元件直接集成在同一封装内,与电子芯片形成 3D 叠加配置,从而实现最小的信号损耗和功耗。

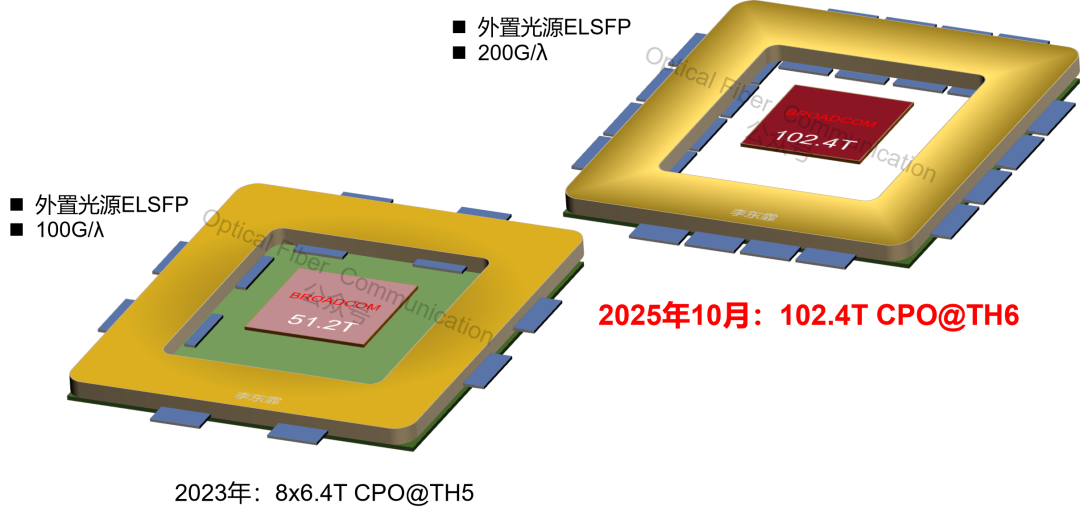

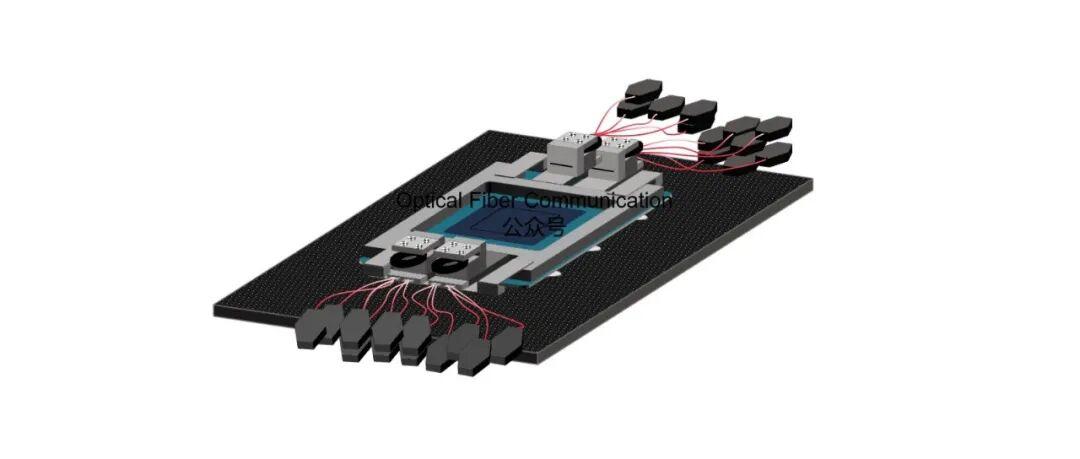

博通的 3D CPO 就是比较典型的应用,它的 PIC 是位于 EIC 之上的倒装芯片,通过基板连接 ASIC。

博通:51.2T CPO 可靠性数据与102.4T CPO 交换机博通&海思:VCSEL NPO/CPO与硅光 CPO另外,在基于玻璃的 3D CPO 方面,EIC、PIC 和玻璃垂直堆叠,侧面装有 ASIC 。英特尔表示,这种技术将用于下一代高功率处理器。关于 CPO 相关的知识与应用可阅读:

Marvell 的 Scale Up/out 的一些观点+102.4T CPO 交换机

感谢阅读!邀请您加入我们的社群,获取大量半导体芯片/光器件/光模块领域的Ebook、技术文档、趋势研报!