近期,英伟达技术路线图中出现的CoWoP已成为半导体行业的热门话题。那么,它与此前备受关注的CoWoS、CoPoS技术相比,究竟有何异同?

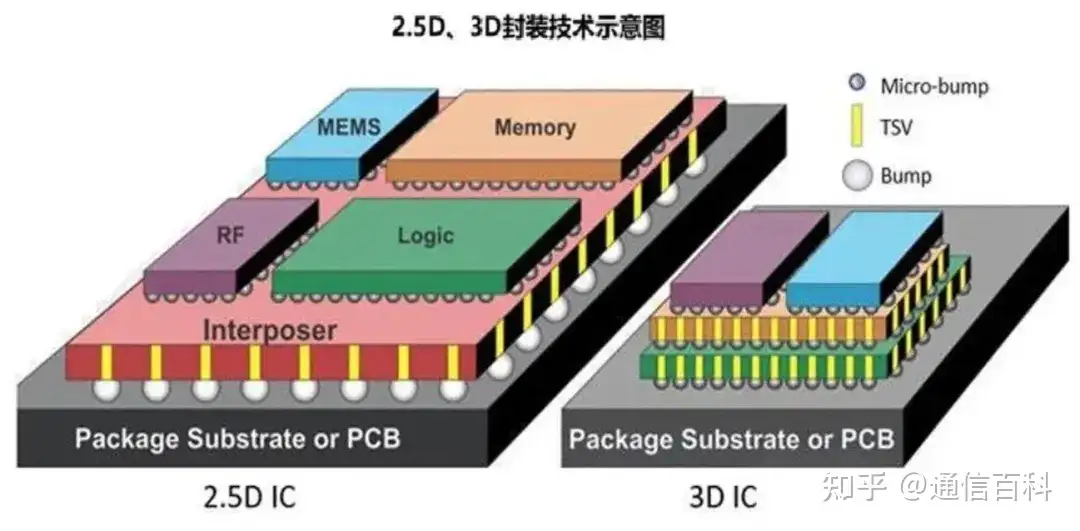

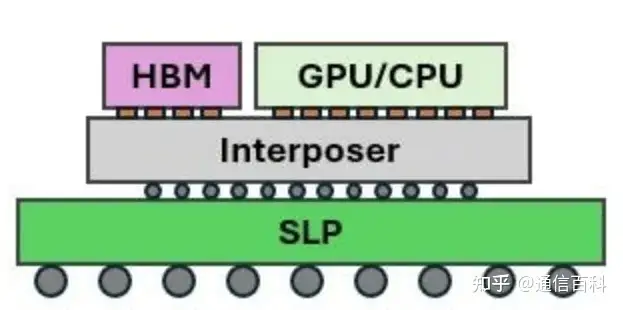

我们知道,传统的2.5D/3D封装技术,通常使用“硅中介层”,通过上面“硅通孔”(TSV)和“再分布层”(RDL)来实现芯片间的高密度连接。

为了不断提升算力和集成度,发展出了三种更先进的技术路径:CoWoS、CoPoS 和 CoWoP。今天我们就来聊一聊这三类技术。

█ CoWoS

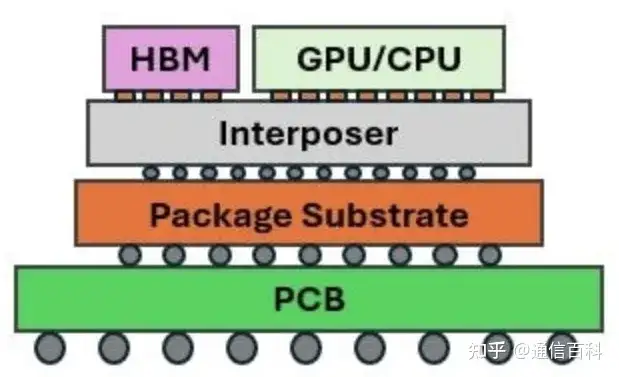

CoWoS(Chip-on-Wafer-on-Substrate):目前的主流技术,像一个“三明治”,从上到下是:硅中介层 → ABF基板 → PCB。

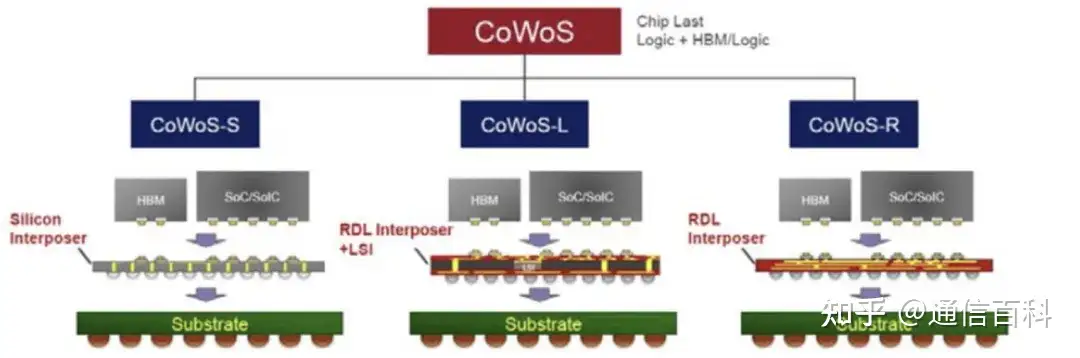

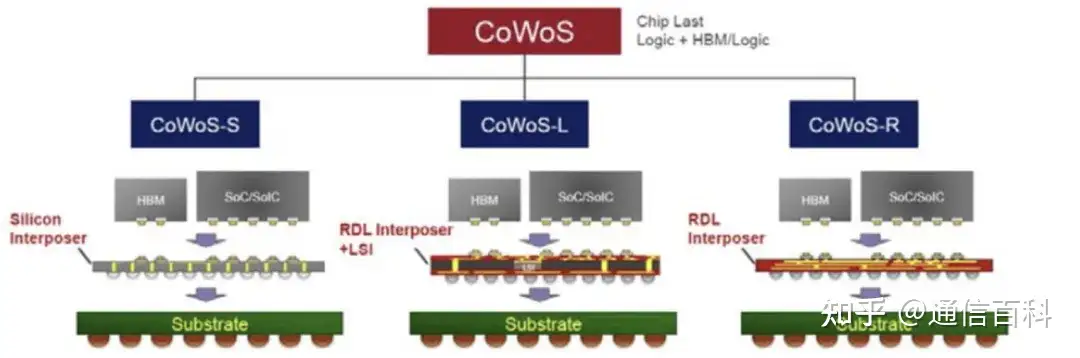

它又根据应用需求演变出几种类型:

- CoWoS-S:使用硅中介层集成HBM与GPU,如英伟达H100;

- CoWoS-R:采用重布线层,面向成本敏感型设计;

- CoWoS-L:结合硅与重布线层,支持多达12颗HBM堆栈的混合方案。

要支撑这种结构,底层的PCB主板必须使用超低损耗的材料(如Megtron 8)和超过28层的复杂叠层设计,以确保高速信号传输的完整性。

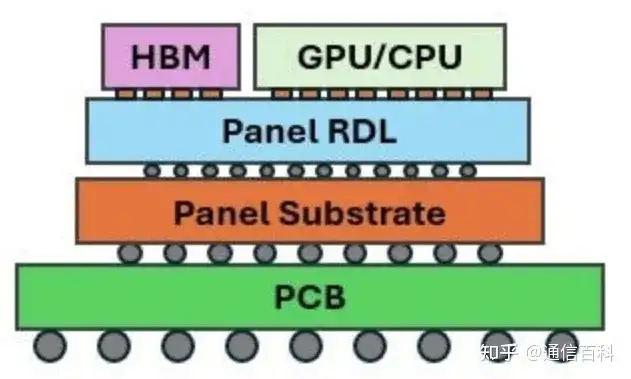

█ CoPoS

CoPoS则通过面板级重布线层(尺寸通常超过600×600mm)替代硅中介层,形成“RDL→ABF基板→PCB”的新型结构。

这样做的好处非常明显:

- 面板利用率从85%提升到95%以上,更经济;

- 成本降低了20-30%;

- 能支持未来AI服务器所需的10-12颗HBM4内存堆栈,提供高达19TB/s的带宽。

█ CoWoP

CoWoP(Chip-on-Wafer-on-PCB),直接将硅中介层绑定于PCB,省去ABF基板。

此方案据说可降低40–50%成本,信号路径更短,支持PCIe 6.0等高速接口,并通过直接接触散热盖提升热管理效能。但它的实现依赖于改良型半加成法(mSAP)工艺,要求PCB实现线宽线距≤25μm、无空隙填孔,并使用超低热膨胀系数材料。

█ 对比

从技术对比来看,三种方案各具优势。

CoWoP虽在成本方面表现突出,但仍面临多项挑战:PCB线宽精度(25μm)落后于ABF基板(≤10μm)、芯片与PCB材料热膨胀系数不匹配,以及生态尚未成熟(目前仅苹果SLP PCB接近其要求)。

这也为PCB材料创新带来机遇:低热膨胀系数玻璃布(如日东纺NE-glass)、可剥离铜箔(如方邦股份)和阳离子树脂等新材料,以及mSAP精细线路加工和填孔电镀(POFV)等新工艺将成为关键突破点。

CoPoS技术要求PCB兼容310×310mm至700×700mm的大尺寸面板,并需支持通过玻璃通孔(TGV)基板实现重布线层集成。

据市场规划,该技术将于2026–2027年建立试点产线(台积电主导),2028年实现量产。而目前主流的CoWoS技术,仍需PCB行业重点解决56+Gbps信号的阻抗控制(偏差需控制在±3%以内),以及40层以上混合FR-4/高速材料的堆叠设计。

对PCB制造商而言,可能需分阶段推进战略布局:

- 短期(2025–2026年):重点满足CoWoS-L所需的18–46层HDI PCB;

- 中期(2027–2028年):与封测厂合作开发CoPoS面板级基板;

- 长期(2029年后):视技术成熟度布局CoWoP产线,服务于边缘计算与AI加速器。

值得注意的是,尽管CoPoS与CoWoP具备显著成本与性能潜力,CoWoS仍是支撑当前AI芯片(如英伟达Rubin平台)的主流技术。

感谢阅读!

推荐阅读: