0.13μm工艺,在半导体领域中指的是晶体管的栅极长度,代表着一个技术节点。我们知道,栅极长度直接影响晶体管的开关速度和电流驱动能力,所以一般来说,我们希望栅极越短越好。

短有很好处,包括:允许在相同面积的硅片上集成更多的电路元件,从而大幅提升了芯片的计算能力和性能。同时更短的栅极长度意味着晶体管可以在更高的频率下工作,同时减小了电流泄漏,从而提高了能效比,以更低的功耗运行。

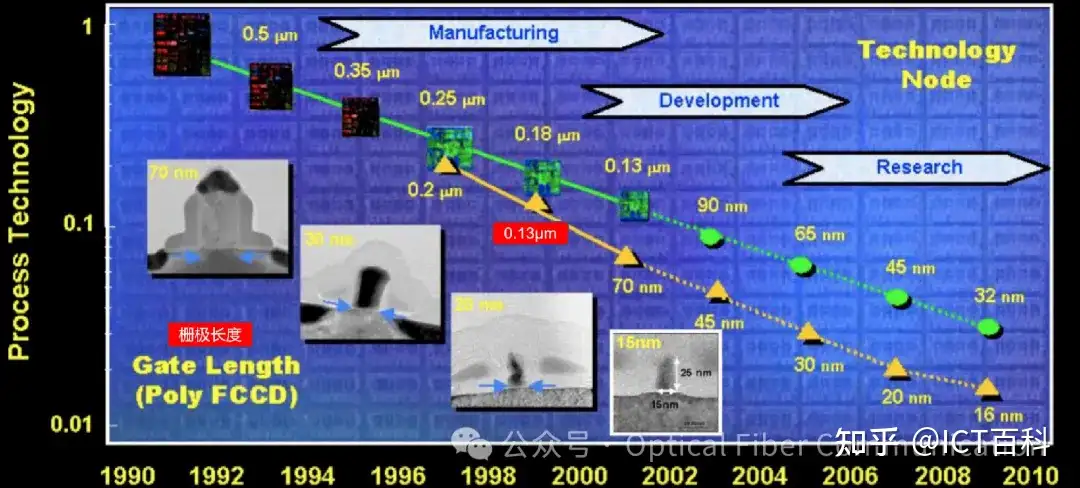

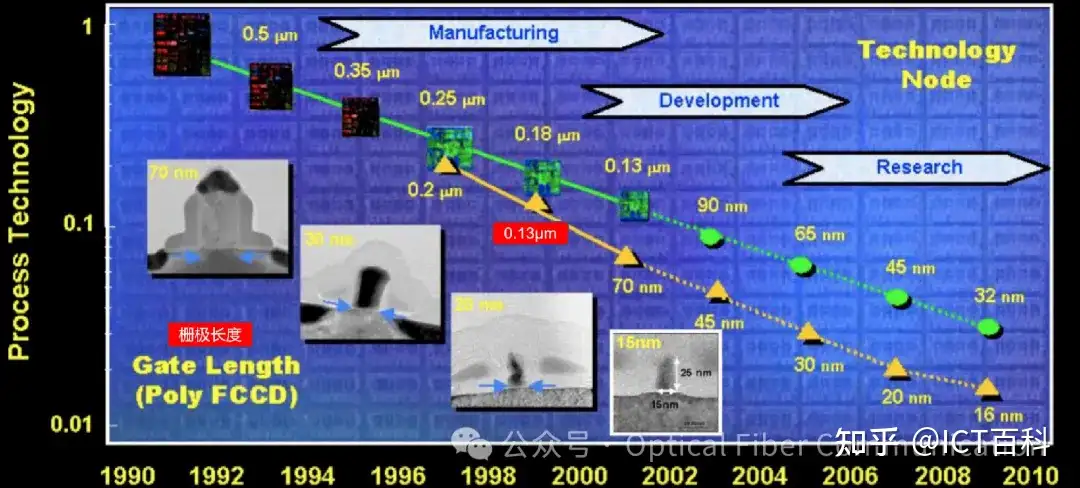

回顾半导体的发展历史,从首次大规模生产MOSFET到1990年代后期,工艺节点或多或少指的是晶体管的栅极长度(Lg),这也被认为是“最小特征尺寸”。例如,英特尔的0.5 μm工艺具有0.5 μm的栅极长度。这种情况一直持续到1997年的0.25 μm工艺,此时英特尔开始引入更激进的栅极长度缩放。例如,他们的0.25 μm工艺具有0.20 μm的栅极长度,同样,他们的0.18 μm工艺具有0.13 μm的栅极长度。如下图是intel早期的半导体Roadmap。

可以看出,在上面这些节点上,描述“工艺节点”的数字实际上大于栅极长度的。工艺节点也被称为技术节点,它描述了半导体制造工艺及其设计规则。在早期,工艺节点的命名直接与晶体管的特征尺寸相关,如栅极长度。

特别是近年来,由于营销策略和不同代工厂之间的差异,节点名称逐渐失去了它的确切含义。例如,22nm、16nm、14nm和10nm等节点,现在更多地代表特定技术制造的特定一代芯片,而不是具体的栅极长度,比如说10nm工艺节点的栅极长度大致在10nm到20nm之间。

当然,这里也是逃不掉摩尔定律的,它预测集成电路上可容纳的晶体管数量大约每两年翻一番。为了实现这一目标,每个新节点的特征尺寸都需要缩小,这一缩放比例大约是0.7倍。具体来说,为了实现密度的倍增,接触式多晶距(CPP)和最小金属间距(MMP)需要每个节点缩放大约0.7倍,可以表示为:0.7x CPP · 0.7x MMP ≈ ½ area

尽管栅极长度的缩小可以带来性能的提升,但在45nm工艺节点之后,栅极长度的缩放基本上停滞了。这是因为随着尺寸的减小,量子效应开始变得更加显著,导致栅极长度的进一步缩小会带来不期望的物理效应,如漏电流的增加和晶体管性能的不稳定。

为了解决这些挑战,英特尔在其 22 纳米工艺中引入 了鳍式场效应晶体管(FinFET),使得晶体管密度继续增加,但栅极长度基本上保持不变。如英特尔的14nm finFET技术中鳍片间距42nm,鳍片高度42nm。10nm工艺中,英特尔的鳍片间距34nm,鳍片高度53nm,这意味着鳍片更高。

随着技术的进步,半节点的概念也应运而生,也称为“node-let”技术。半节点代表了在完整的工艺节点之间的增量改进,通常涉及0.9倍的线性缩放。

比如说在从90nm工艺过渡到65nm工艺的过程中,可能出现78nm或70nm的半节点产品。包括现在现在已有10nm和7nm的全节点工艺以及5nm和3nm工艺之间,引入12nm,11nm,8nm,6nm和4nm等半节点技术。虽然不清楚是否所有的节点工艺都会长期存在,但是这种node-let技术允许制造商在不完全进入下一个全节点工艺的情况下,通过一些改进和优化,提升芯片的性能和能效。

总之,从0.13um工艺节点到今天的7nm、5nm,以及未来可能的更小尺寸,栅极长度都不再是工艺节点命名的直接依据,但它仍然是衡量晶体管尺寸和性能的关键参数。

感谢阅读!